## Centro de Investigación y de Estudios Avanzados del Instituto Politécnico Nacional Departamento de Ingeniería Eléctrica Sección de Computación

# Hardware Level Description of Dynamic Programming Algorithms

Tesis que presenta el M. en C. Arturo Díaz Pérez para obtener el grado de Doctor en Ciencias dentro de la especialidad en Ingeniería Eléctrica con opción en Computación. Trabajo dirigido por el Dr. Guillermo Morales Luna.

A Mary, Carmelita, y Lilí

A mis padres,

a mis hermanos,

y a mis sobrinos

#### ACKNOWLEDGEMENT

Many people have been involved in the elaboration of this thesis. To all of them the only thing I can say is thank you. However, some people deserve special considerations from me:

to Guillermo Morales Luna for having confidence on my research and helping me during all the stages of this investigation. For accepting to mentor me and teach me, for working with me on a day to day basis, and for being a very good friend;

to Mike Quinn for accepting me at his lab, for being willing to work with me under unusual circumstances during that unforgettable year I spent at OSU. His multiple comments and opinions have greatly influenced the results of this research;

to Sanjay Rajopadhye for introducing me the fundamental theory of systolic arrays;

to Sergio Rajsbaum, Adriano de Luca, Bill Taffe and Isidoro Gitler for accepting to serve on my committee and for the time they spent in my behalf;

to Sergio Chapa for all support he offered me during my stay at the Sección de Computación;

to CINVESTAV for giving me facilites and support to finish this investigation;

to my little girls Carmelita and Lilí for the time and love we sacrificed because of this research;

and finally to my wife Mary for her constant love and unconditional support.

This work was undirectly supported by CONACyT with the scholarship 68102.

#### Resumen

Los arreglos de compuertas programables (FPGAs por sus siglas en inglés), se han usado de manera exitosa como procesadores configurables en algunas aplicaciones. Algunas aplicaciones han rebasado el rendimiento ofrecido por sistemas de cómputo de propósito general. Desafortunadamente, la tecnología actual de FPGAs presenta una serie de limitaciones de manera que éstos no pueden aplicarse de forma arbitraria para cualquier tipo de algoritmos. Para implementar algoritmos en FPGAs uno debe ir desde una descripción de alto nivel del algoritmo hasta secuencias de digitos binarios (bits) que representa el diseño para configurar uno o posiblemente varios FPGAs. La mayoría del trabajo actual se ha enfocado a los aspectos de bajo nivel de este enfoque, esto es, al desarrollo de herramientas para generar diseños de circuitos a implementarse en FPGAs. La entrada de este enfoque es usualmente, una descripción de un algoritmo a un nivel muy bajo. En esta tesis, presento una metodología de diseño para implementar algoritmos en FPGAs a partir de descripciones de alto nivel. Dado que los FPGAs no pueden ser aplicados para implementar algoritmos arbitrarios, esta metodología se restringe a la clase de algoritmos de programación dinámica cuya importancia ha sido probada de manera extensa. La metodología parte de un algoritmo de programación dinámica escrito en el lenguaje de programación C\* y termina produciendo un diseño de un circuito en el lenguaje de descripción de circuitos VHDL. En las etapas intermedias, se obtienen las ecuaciones de recurrencia que describen el comportamiento funcional del programa y esta ecuaciones se llevan, cuando es posible, a una forma uniforme. A partir de ecuaciones uniformes se obtienen representaciones que configuran un arreglo de procesadores (espacio) en diferentes instantes de tiempo. El diseño de un circuito en VHDL se obtiene a partir de las representaciones espacio-tiempo.

#### Abstract

Field programmable gate arrays (FPGAs) have been successfully applied as computing engines for some applications. Some of them have outperformed large-scale general-purpose computing systems. However, current FPGA technology imposes a number of limitations that severely restrict the class of algorithms FPGAs are useful for. In implementing algorithms for FPGAs one must go from an algorithmic description to binary files which represent a design to configure one, or possibly more, FPGAs. Most of the current work has been focused on the low-level aspects of this approach, i.e., in the tools to generate circuit design to implement algorithms in FPGAs. The input of this approach is usually an enough low-level description of an algorithm. In this thesis, I present a design methodology whose main concern is on the high-level aspects of algorithm implementation for FPGAs. Since currently FPGAs cannot be used for implementing arbitrary algorithms, I restrict myself to the class of dynamic programming algorithms. The importance of dynamic programming has been proved elsewhere. I start from a dynamic programming program written in a parallel language, C\*, and a circuit design in a hardware description language, VHDL, is produced. In the middle, it is obtained the recurrence equations that describe the functional behavior of the program, these equations are transformed to a uniform shape, and, finally, space-time descriptions are produced from which the design in VHDL is generated.

# Contents

| 1 | Int  | roduction                                                   |

|---|------|-------------------------------------------------------------|

|   | 1.1  | FPGA Characteristics and Limitations                        |

|   | 1.2  | Custom Computing Review                                     |

|   | 1.3  | Our Approach                                                |

|   | 1.4  | Summary of Major Contributions                              |

|   | 1.5  | Overview of the Thesis                                      |

| 2 | Δ (  | Classification of Dynamic Programming Algorithms            |

| ~ | 2.1  | Introduction                                                |

|   | 2.2  | Dynamic Programming Formulations                            |

|   | 2.3  | Classification of DP Algorithms                             |

|   | 2.4  | Some Examples of DP Problems                                |

|   | 2. 1 | 2.4.1 The Shortest-Path Problem                             |

|   |      | 2.4.2 The Knapsack Problem                                  |

|   |      | 2.4.3 Longest Common Subsequence                            |

|   |      | 2.4.4 Edit Distance                                         |

|   |      | 2.4.5 Gap Problem                                           |

|   |      | 2.4.6 RNA Problem                                           |

|   |      | 2.4.7 Least Weight Subsequence                              |

|   |      | 2.4.8 All-Pairs Shortest Paths                              |

|   |      | 2.4.9 Optimal Matrix Parenthesization                       |

|   | 2.5  | Dynamic Programming Remarks                                 |

|   | 2.6  | Conclusions                                                 |

|   |      |                                                             |

| 3 |      | a-Parallel Dynamic Programming                              |

|   | 3.1  | General Guidelines                                          |

|   | 3.2  | C* Programming Model                                        |

|   | 3.3  | A Straightforward Approach for Parallel Dynamic Programming |

|   |      | 3.3.1 Data-parallel loops of DP problems                    |

|   | 3.4  | A Practical Approach for Parallel Dynamic Programming       |

|   |      | 3.4.1 Uniform Dependencies                                  |

|   |      | 3.4.2 Non-uniform Dependencies                              |

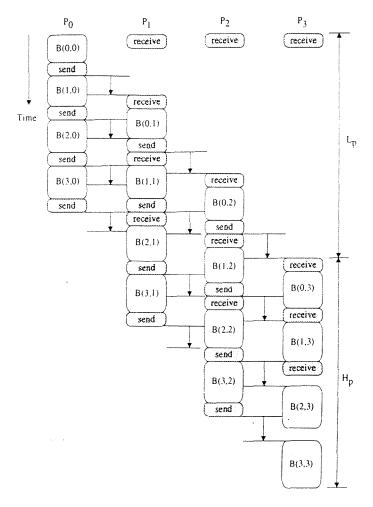

|   | 3.5  | A Block Decomposition Scheme for a Class of DP Algorithms   |

|   |      | 3.5.1 Gap Problem                                           |

|   |      | 3.5.2 Block Decomposition for the Gap Problem               |

|   |      | 3.5.3 Homogeneous Block Decomposition                       |

|   |      | 3.5.4 Non-Homogeneous Block Decomposition                   |

|   |      | 3.5.5 Discussion                                            |

|   | 3.6  | Related Work                                                |

|   | 3.7  | Conclusions                                                 |

| 4 | Red      | currence Equations 4                                   | ] |

|---|----------|--------------------------------------------------------|---|

|   | 4.1      | Introduction                                           |   |

|   | 4.2      | Recurrence Equations                                   |   |

|   | 4.3      | Equation and Identifier Domains                        | 2 |

|   | 4.4      | Notation                                               |   |

|   | 4.5      | Dependence Relation                                    |   |

|   | 4.6      | Recurrence Equations Special Cases                     |   |

|   | 4.7      | Generating Space-Time Descriptions                     |   |

|   | 4.8      | Conclusions                                            |   |

|   |          |                                                        |   |

| 5 | Dat      | taflow Analysis of Parallel Expressions in C* 4        | 7 |

|   | 5.1      | Introduction                                           | 7 |

|   | 5.2      | Definitions and Notation                               | 8 |

|   |          | 5.2.1 Affine C* Program Fragment                       | 8 |

|   |          | 5.2.2 Notation                                         | 8 |

|   |          | 5.2.3 Domain of Parallel Variables                     | ĉ |

|   |          | 5.2.4 Source Function                                  | 9 |

|   |          | 5.2.5 Flow Dependency                                  | 9 |

|   |          | 5.2.6 Sequencing Predicate                             | 0 |

|   |          | 5.2.7 Dataflow Dependency Relation                     | J |

|   | 5.3      | Deriving Recurrence Equations                          | J |

|   |          | 5.3.1 Shortest-Path Problem                            | 1 |

|   |          | 5.3.2 Longest Common Subsequence                       | 3 |

|   |          | 5.3.3 All-Pairs Shortest Path                          |   |

|   |          | 5.3.4 Optimal Matrix Parenthesization                  | 5 |

|   | 5.4      | Related Work                                           |   |

|   | 5.5      | Conclusions                                            | 7 |

| _ | <b>1</b> |                                                        |   |

| 6 |          | Uniformization of Recurrence Equations 59              |   |

|   | 6.1      | Introduction                                           |   |

|   | 6.2      | A Transformation as The Basic Block                    |   |

|   | 6.3      | A Set of Useful Transformations                        |   |

|   |          | 6.3.1 Variable Manipulation                            |   |

|   |          | 6.3.2 Domain manipulation                              |   |

|   |          | 6.3.3 Computation manipulation                         |   |

|   | 6.4      | The Convolution Problem                                |   |

|   | 6.5      | The Transitive Closure Problem                         | ŧ |

|   | 6.6      | Uniformization of the Gap Problem                      |   |

|   | 6.7      | A Tool for Manipulating Recurrence Equations           |   |

|   | 6.8      | Conclusions                                            |   |

| 7 | Con      | erating VHDL Behavioral Models 81                      |   |

| • | 7.1      | erating VHDL Behavioral Models 81 Introduction         |   |

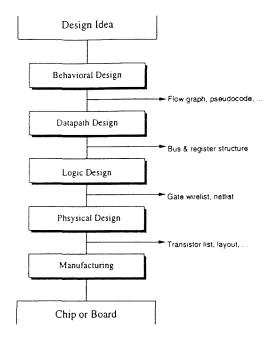

|   | 7.2      | Digital Design Process Review                          |   |

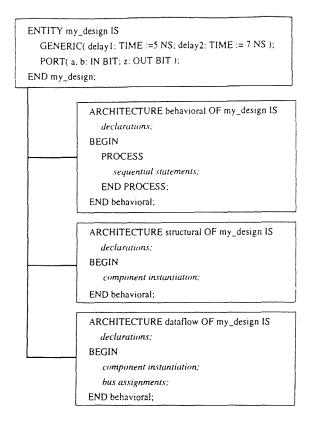

|   | 7.3      | VHDL Review                                            |   |

|   | 7.4      | Space-Time Descriptions                                |   |

|   |          |                                                        |   |

|   | 1.0      | Important Issues in Generating Behavioral Descriptions |   |

|   |          | 7.5.2 Obtaining a Generic Processor                    |   |

|   |          | 7.5.2 Obtaining a Generic Processor                    |   |

|   |          |                                                        |   |

|   |          |                                                        |   |

|   |          |                                                        |   |

|   |          | 7.5.6 Condition Evaluation                             |   |

|   |          | TOUR STERELARINE THE REPUBLIC POLESSON MILAY           |   |

~ .

|   | 7.6 A Case Study: The Edit Distance |     |

|---|-------------------------------------|-----|

| 8 | Conclusions                         | 97  |

|   | 8.1 Review of Goals                 | 97  |

|   | 8.2 Open Problems and Future Work   | 98  |

|   | 8.3 Final Considerations            | 99  |

| A | Acronyms                            | 101 |

vi

# List of Figures

| 1.1        | Translating $C^*$ to hardware description level                                                                                        |    |

|------------|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2        | A typical view of an FPGA                                                                                                              | ,  |

| 1.3        | The configuration logic block of the Xilinx 4000 FPGA Series                                                                           | 4  |

| 1.4        | Approaches to custom computing.                                                                                                        | (  |

| 1.5        | Translation C* to hardware description level                                                                                           | •  |

| 2.1        | Dynamic programming problems classification and examples                                                                               | 1  |

| 2.2        | A multistage graph for the shortest-path problem.                                                                                      | 13 |

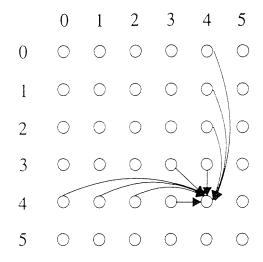

| 2.3        | Dependencies of the knapsack problem.                                                                                                  | 15 |

| 2.4        | An example of the longest common subsequence problem                                                                                   | 15 |

| 2.5        | Dependencies in the Edit Distance Problem                                                                                              | 16 |

| 2.6        | Dependencies of the gap problem                                                                                                        | 17 |

| 2.7        | Dependencies of the RNA problem                                                                                                        | 18 |

| 2.8        | The least weight subsequence problem                                                                                                   | 19 |

| 2.9        | An example of the all-pairs shortest paths problem                                                                                     | 20 |

| 2.10       | An instance of the optimal matrix parenthesization problem.                                                                            | 21 |

| 3.1        | The C* Programming Model                                                                                                               | 24 |

| 3.2        | Organization of the shortest path problem by levels                                                                                    | 26 |

| 3.3        | The longest common subsequence DP table and dependencies                                                                               | 27 |

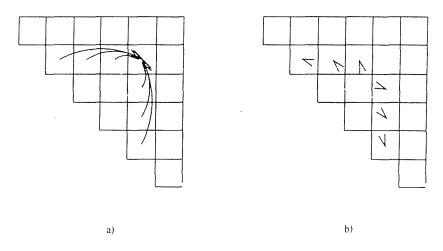

| 3.4        | Wavefront for the optimal matrix parenthesization problem                                                                              | 28 |

| 3.5        | Dependencies of the gap problem                                                                                                        | 32 |

| 3.6        | Block decomposition of the Gap Problem                                                                                                 | 32 |

| 3.7        | The parallel execution of the block decomposition scheme for the Gap Problem al-                                                       |    |

|            | lowing overlap of computations with communications.                                                                                    | 33 |

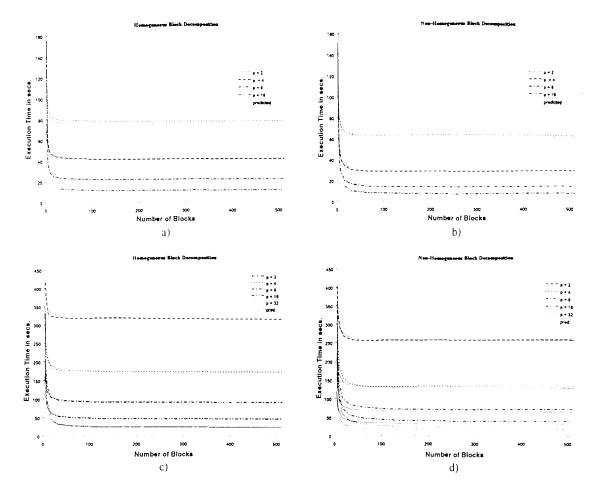

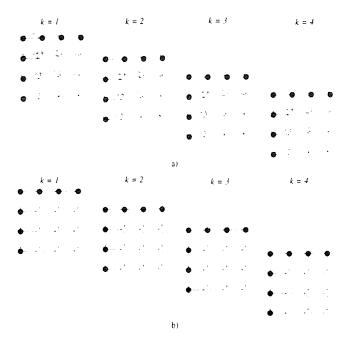

| 3.8        | Effect of the number of blocks int the execution time on the Meiko CS-2 a y b, and                                                     |    |

|            | on the CM-5 c and d. a) and b) show homogeneous block decomposition. b) and d)                                                         |    |

|            | show non-homogeneous block decomposition.                                                                                              | 38 |

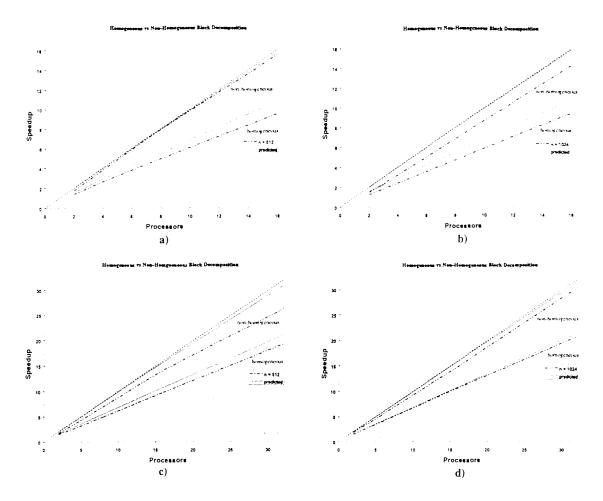

| 3.9        | Speedup of homogeneous and non-homogeneous decomposition schemes on the Meiko CS-2 on the CM-5. a) and c) $n=512$ . b) and d) $n=1024$ | 39 |

| 5.1        | General shape of code segments being analyzed in the dataflow analysis algorithm.                                                      | 48 |

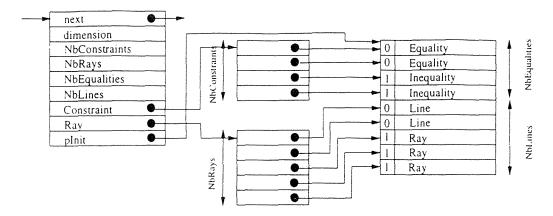

| 6.1        | The data structure used to represent unions of polyhedra                                                                               | 61 |

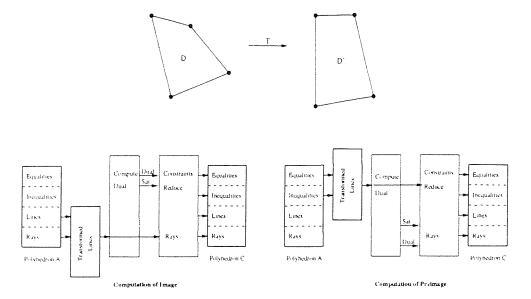

| 6.2        | A linear transformation, image, of domain $D$ into $D'$ uses the parametric representa-                                                |    |

|            | tion. The inverse transformation, pre-image, is computed from the implicit represen-                                                   | 62 |

| 6.3        | Serialization of an expression with a non-fixed number or parameters.                                                                  | 62 |

| 6.3        | Pipelining of a value used in multiple domain points.                                                                                  | 63 |

| 6.4<br>6.5 | a) The initial index domain for each variable of the convolution problem. b) The                                                       | və |

|            | values required at each index point of $y_i$                                                                                           | 63 |

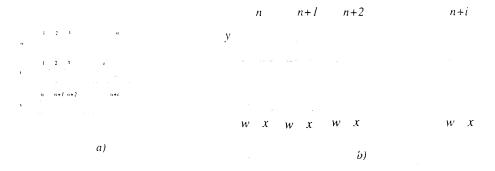

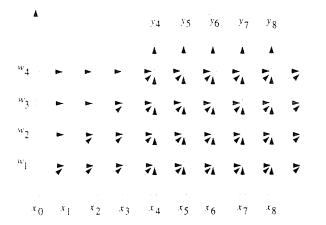

| 6.6        | Serialization of $\sum_{k=1}^{N} w_k x_{i-k}$ in the convolution problem                                                               | 64 |

| 6.7  | Pipelining $x$ and $w$ values for the convolution problem                              | 65 |

|------|----------------------------------------------------------------------------------------|----|

| 6.8  | A different result for the convolution problem changing the positions of alignment and |    |

|      | directions of serialization and pipelining.                                            | 66 |

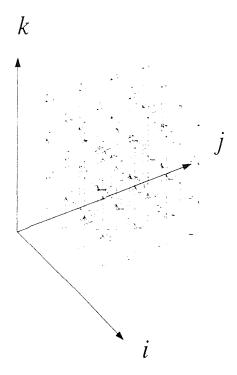

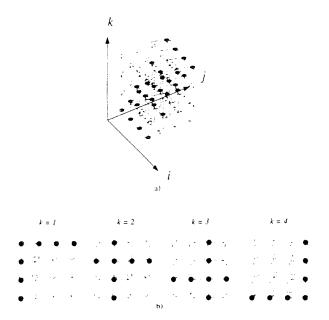

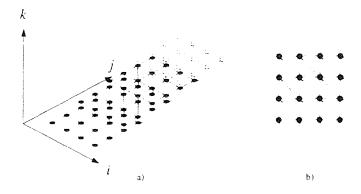

| 6.9  | a) A 3D view of the dependencies in the transitive closure problem. b) A view by       |    |

|      | planes of the dependency graph.                                                        | 67 |

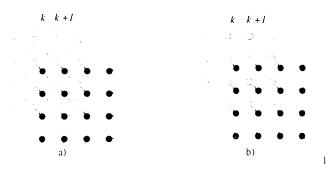

| 6.10 | Localization communications lying in the same k-plane. a) A view by planes. b) A       |    |

|      | 3D view                                                                                | 68 |

| 6.11 | Domain splitting and translation proposed to uniformize the dependence directions      |    |

|      | within each plane shown in Fig. 5a                                                     | 69 |

| 6.12 | Dependency graph obtained first by applying the domain transformation (Fig. 6.11)      |    |

|      | and then by applying the localization step (Fig. 6.10)                                 | 70 |

| 6.13 | a) Changing in dependency vectors between subsequent k-planes. b) Localization         |    |

|      | long communications (see text)                                                         | 70 |

| 6.14 | a) 3D view of the transformed dependency graph. b) A projection of the domain onto     |    |

|      | the $(1,1,1)^T$ direction                                                              | 71 |

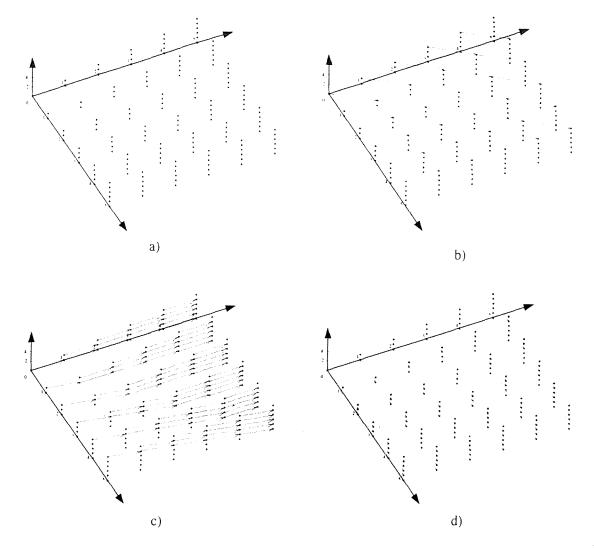

| 6.15 | Uniformization process of the gap problem. a) The extended 3D domain. b) Depen-        |    |

|      | dencies obtained by the D[i-1,j-1] term. c) Propagation of the values along rows. d)   |    |

|      | Propagation of values along columns                                                    | 75 |

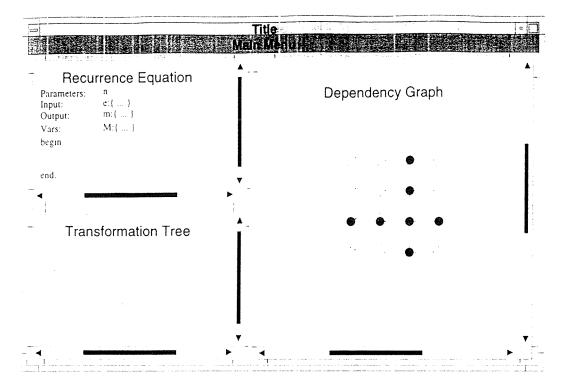

| 6.16 | a) The transformation library, b) the navigation tree, and c) the graphical output.    | 77 |

|      | The main screen of the tool to manipulate recurrence equations.                        | 78 |

| 6.18 | An example partitioning and translation transformations using direct manipulation.     | 79 |

| 7.1  | A typical abstraction hierarchy of the digital design process                          | 82 |

| 7.2  | A typical VHDL with alternative descriptions.                                          | 83 |

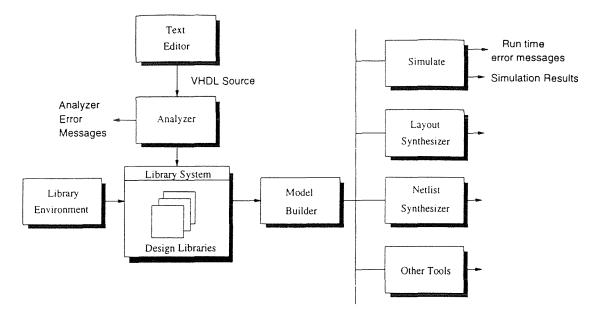

| 7.3  | A VHDL working environment                                                             | 84 |

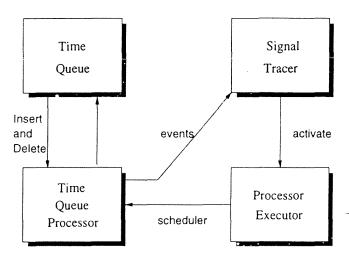

| 7.4  | A typical VHDL simulator                                                               | 84 |

| 7.5  | A typical behavioral VHDL description of a generic processor                           | 89 |

| 7.6  | A generic parameter to indicate processor identification.                              | 90 |

| 7.7  | Use of temporal signals for handling delays.                                           | 91 |

| 7.8  | A typical process model to compute the value of a variable in a clock cycle            | 92 |

| 7.9  | VHDL model for a linear processor array using the iterative features of VHDL           | 93 |

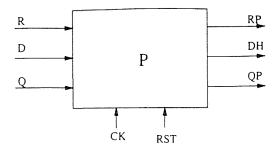

| 7.10 | Port configuration of the generic processor for the edit distance problem              | 94 |

|      | Port configuration of the generic processor for the edit distance problem              | 94 |

|      | Process model of variable $R$ of the generic processor for the edit distance problem   | 95 |

|      | Process model of variable $D$ of the generic processor for the edit distance problem.  | 95 |

| 7.14 | Process model of variable $Q$ of the generic processor for the edit distance problem.  | 95 |

## List of Tables

| 1.1 | Density and performance for common circuit functions | 5  |

|-----|------------------------------------------------------|----|

| 2.1 | A set of dynamic programming algorithms.             | 12 |

### Chapter 1

### Introduction

Performance is a continuing concern in the design of computer-based systems. Advances to enhance performance can be broadly placed into two main categories: technological and architectural. Technological advances involve finding new materials and techniques to make gates that switch faster and memories that can be accessed faster. Architectural advances involve reorganizing these gates and memories to allow more operations to occur at the same time. Until the mid 90's, technological advances dominated increases in speed. However, the technology is approaching fundamental limits. Future increases in performance will be forced to rely more heavily on advances in computer architecture.

One of the primary methods for gaining performance-improvement based on the possibilities of the latest VLSI technologies is to migrate functions or parts of functions to auxiliary special purpose processors and controllers dedicated to a specific application area or algorithm. The first examples of such an approach were application-specific integrated circuits (ASICs). Their applications are varied. They rank from digital signal processing applications to neural networks implementations and special controllers. However, ASICs are inflexible which has limited their use. Moreover, the time and cost to design and build an ASIC have prevented its applicability.

Some kind of circuits were proposed for general-purpose applications. The most successful examples of that are probably the VLSI array processors used for signal processing [50]. Although array processors have several advantages, ASICs restrictions have limited their use. Those restrictions have been partially broken with the rise of field-programmable gate arrays (FPGA) [63]. Currently, FPGA technology provides an alternative for implementing application-specific circuits without the non-recurring engineering cost associated with ASICs.

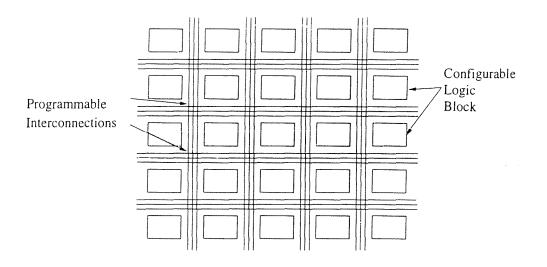

An FPGA is an IC consisting of user-programmable logic blocks (CLBs) and interconnection fabric that can be used in the design of a digital circuit [73]. Any kind of digital circuit can be implemented using FPGAs. Each block in the circuit is user-programmable, meaning that the functionality implemented by the block can be determined by the user after the block has been fabricated. Many FPGAs providers exist, among the best known are Xilinx [82], Altera [5], Actel [1] and Algotronix [4].

FPGAs were first applied to logic design. Hence numerous tools were provided for synthesizing logic designs for FPGAs. Hardware description languages (HDL) and diagram editors have been used as a starting point for such a process. Many hardware description languages exist; each company has developed its own. Verilog and VHDL are among the most popular languages we can find [59]. To avoid implementing every design from scratch, most providers offer several libraries of predefined devices or modules from which a design can be built.

Recently, FPGAs have been used for custom computing where the goal is obtaining improvements in performance by implementing algorithms in hardware at reasonable cost. The main advantage of FPGAs is their reconfigurability, i. e., they can be used for different purposes at different stages of a computation. Numerous reconfigurable architectures based on FPGAs have already been built [8, 14, 28, 36]. Some of them have outperformed large-scale general-purpose computing systems for some applications [36]. Those applications have demonstrated that FPGAs can be integrated in

scalable architectures.

Each individual CLB of an FPGA has a limited logical complexity. Although FPGA density has greatly increased in recent years\*, the aggregate non-integral compute power of an FPGA chip is relatively low. Current FPGA technology imposes several limitations that severely restrict the class of algorithms FPGAs are useful for. DeHon [25] provided examples of algorithms well suited for reconfigurable engines. For this reason, only some sets of applications—those working at the bit level or using fixed point arithmetic—can lead to levels of performance superior to conventional, readily available CPUs. An approach to overcome with this limitation is to have reconfigurable computing engines organized with arrays of FPGAs. That exhibits new restrictions to make effective use of FPGA area. Local and regular communications are desirable properties of FPGA algorithmic applications.

In spite of the current limitations, I believe that FPGA density will increase in the future to allow more complicated functions be implemented on them. When that technology eventually becomes available, tools and techniques will be required to effectively use FPGAs as custom computing engines.

As the number and the density of FPGAs increase, the task of developing custom circuits for each FPGA in the system becomes enormous. In addition, the lack of knowledge and tools necessary to develop reconfigurable applications further obstructs general purpose implementation. A strong background in hardware development is required as well as expensive CAD and synthesis tools. Until reconfigurable systems address the deficiencies of large-scale application development, reconfigurable logic will remain in the application-specific realm.

In order for reconfigurable systems to become general purpose computing systems, they must be easy to program and use. Although some early work has been done on automated software/hardware co-synthesis [2], most reconfigurable systems are programmed using conventional hardware development techniques such as schematic capture or hardware description languages. However, hardware description languages are very low level languages for describing algorithms, therefore, most of the custom computing research has been focused on the low-level aspects of algorithm implementation in FPGAs.

One way to reduce the problem of realizing custom circuitry on reconfigurable hardware systems is to develop tools and techniques for the hardware implementation of algorithms starting from high level descriptions. That involves on the one hand, developing compiling techniques for the synthesis of programs to hardware description languages, and on the other hand, characterizing the applications susceptible to take advantage of that approach. This research considers the high-level aspects of algorithm implementation for reconfigurable engines and address these two questions providing a general framework to face those problems.

The main objective of this dissertation is to present a methodology for the synthesis of algorithms from high-level specifications to hardware description level. It is considered, on the one hand, the limitations of FPGAs, and on the other hand, some techniques developed for synthesizing processor arrays.

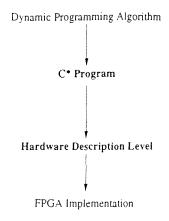

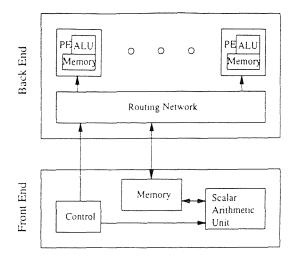

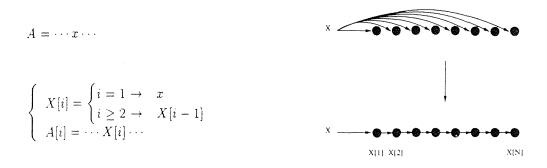

I propose to use the C\* parallel programming language as a high level specification of programs to be implemented in FPGAs and to use VHDL as a target language as it is shown in Figure 1.1. C\* is based on a synchronous SIMD model (data-parallel) of computation with a global name addressing mechanism. VHDL has become a standard language for circuit implementation. On one side, previous research has demonstrated that data-parallel programs can be compiled and efficiently executed on both SIMD and MIMD parallel computers [40]. On the other side, numerous commercial tools exist to implement circuits from VHDL.

My main interest here is to determine how to apply the data-parallel paradigm to FPGA computing. Some other works, dealing with bit-level applications, have tried to develop compilation techniques to derive hardware descriptions from high level programming languages [37, 8]. Considering the FPGA scalability and characteristics, my goal here is showing how to derive regular processor arrays for FPGA computing from some data-parallel algorithms expressed in the C\* programming language.

<sup>\*</sup>Altera has announced a new series of FPGA having until 200K reconfigurable gates

Figure 1.1: Translating C\* to hardware description level.

Figure 1.2: A typical view of an FPGA.

#### 1.1 FPGA Characteristics and Limitations

As was pointed out before, the main feature of FPGAs is their re-programmability. FPGAs are general-purpose circuits capable of implementing any digital circuit. The logic blocks of FPGAs may consist of combinatorial or sequential logic elements. The blocks can be connected after fabrication in a general way using a programmable routing fabric. This routing fabric consists of programmable switches that connect various horizontal and vertical routing segments together with the pins from logic blocks [78] (See Figure 1.2). The logic blocks architecture available in commercial FPGAs ranges from fine grain to coarse grain blocks. The interconnection re-programmability is based on either static RAM or antifuse technology [38].

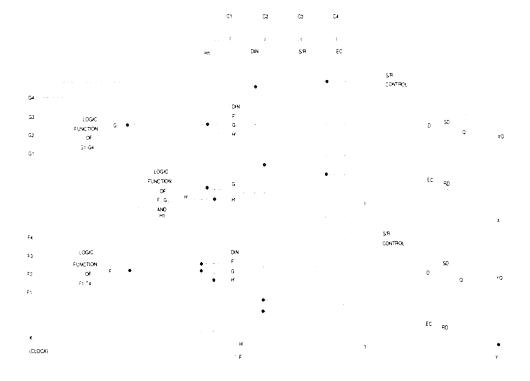

In Figure 1.3 we show the CLB of the Xilinx 4000 FPGA series. Each CLB contains a pair of flip-flops and two independent 4-input function generators. The flip-flops can be used to store the function generators outputs or they can be used independently. A third function generator with three inputs is provided. One or both of these inputs can be the outputs of the 4-input function generators; the other input(s) can be from outside the CLB. The CLB can therefore implement any of the following functions: (1) two functions of up four variables, plus any third function of up three unrelated variables, (2) any single function of up five variables, (3) any function of four variables together with some functions of six variables, and (4) some functions of up nine variables.

Implementing wide functions in a single block reduces both the number of blocks required and the delay in the signal path, achieving both increased density and speed. The versatility of the CLB

Figure 1.3: The configuration logic block of the Xilinx 4000 FPGA Series.

function generators significantly improves system speed. In addition, design-software tools can deal with each function generator independently which improves cell usage.

The XC4013E model of Xilinx FPGA series contains a matrix of  $24 \times 24$  CLBs. That produces 567 CLBs which can store up to 13,000 gates and 1,536 flip-flops. In table 1.1 we show some common circuit functions, the number of CLBs they occupy and the speed of the circuit.

As can be observed, the density and speed of different functions is varied. Currently, the main disadvantage is the low density of logic blocks per area unit available with present VLSI technology. Due to this there are some interesting circuits that can not be successfully implemented for array processors. For example

- Floating-point arithmetic is severely limited for FPGAs because it would require wide area on the circuit. Trying to implement arrays of floating point functional units would not be easy.

- Large and variable interconnectivity would be restricted due to delays involved in the interconnection architecture of FPGAs.

- Extremely fast applications possibly would not be suitable for FPGAs due to delays present in their architecture.

Regardless above restrictions, FPGAs can be properly used for rapid prototyping algorithms at the hardware level. Considering the restrictions of FPGA applications, the desirable properties of potential FPGAs applications would be:

- 1. To use only integer arithmetic or at most low precision fixed point arithmetic.

- 2. To consist of logical operations to make decisions. Comparators, selectors and multiplexers are good examples of that.

- 3. To be capable of being decomposed in independent and pipelined stages.

- 4. To have regularity in the way processing is applied.

| Design Class | Function                                 | CLB used | Speed/Units |

|--------------|------------------------------------------|----------|-------------|

| Memory       | 256x8 Single Port (read/modify/write)    | 72       | 63 Mhz      |

| Memory       | 32x16 bit FIFO (simultaneous read/write) | 48       | 63 Mhz      |

| Memory       | 32x15 bit FIFO (MUXed read/write)        | 32       | 63 Mhz      |

| Logic        | 9 bit Shift Register (with enable)       | 5        | 170 Mhz     |

| Logic        | 16 bit Pre-Scaled Counter                | 8        | 142 Mhz     |

| Logic        | 16 bit Loadable Up/Down Counter          | 8        | 70 Mhz      |

| Logic        | 16 bit Accumulator                       | 9        | 70 Mhz      |

| Logic        | 8 bit, 16 tap FIR filter (parallel)      | 400      | 55 Mhz      |

| Logic        | 8 bit, 16 tap FIR filter (serial)        | 68       | 8.1 Mhz     |

| Logic        | 8x8 Combinatorial Parallel Multiplier    | 68       | 22.8 ns     |

| Logic        | 16 bit Address Decoder (internal decode) | 3        | 4.7 ns      |

| Logic        | 9 bit Parity Checker                     | 1        | 4.3 ns      |

Table 1.1: Density and performance for common circuit functions

5. To have locality in the interconnection network they require. That means that they have only interconnections with their neighbors.

Considering FPGA capabilities and limitations some potential applications for FPGAs are:

- 1. Image processing algorithms such as point type operations (grey scale transformation, histogram equalization, requantization, etc.) and filtering (template matching, window techniques, convolution/correlation, median filtering, etc.) seem to be good candidates for FPGA implementation.

- 2. Dynamic programming algorithms requiring only integer arithmetic. Dynamic programming is in essence a bottom up procedure in which solutions to all subproblems are first calculated and the results used to solve the whole problem. A good example of this approach is the Floyd's shortest path algorithm.

- 3. Relaxation techniques requiring fixed point arithmetic. The relaxation technique is an iterative approach to many problems, which makes updating in parallel at each point and in each iteration based on the data available in the most recent updating or in the immediate preceding iteration.

- 4. Associative retrieval operations. Filling and retrieving data by association appears to be a powerful solution to many high volume information processing elements. An associative processing system is very adequate for recognition and recall from partial information and has remarkable error correcting capabilities. The major advantage of associative memory over RAM is its capability of performing parallel search and parallel comparison operations. There many examples of that kind of applications: pattern matching, artificial intelligence, computer vision, data encoding, compression, and every application maintaining a dictionary data structure.

#### 1.2 Custom Computing Review

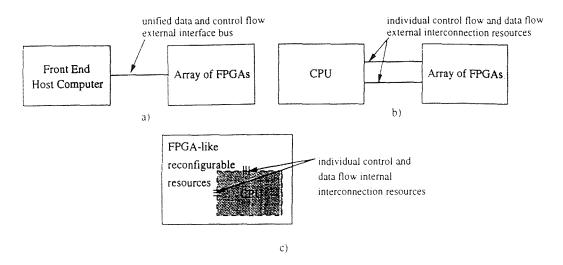

The general idea of custom computing is to add a co-processor to a common processor to serve in the execution of some parts of a program. Given that co-processors built with FPGAs are reconfigurable, then such co-processors can be configured to execute different functions at different times of the program execution. Several custom computing machines have been proposed. They can be classified in one of three different approaches as it is shown in Figure 1.4. In Figure 1.4a we show the most common configuration for a custom computing machine. An array of FPGAs is

Figure 1.4: Approaches to custom computing.

used within a host computer; they are configured through the internal bus. In the same manner, control signals, data and results flow through the host bus. Performance is limited here by the bus bandwidth to transfer data. The best known and most successful machines have this configuration. Some examples are Splash [36], DEC Perle [28], and AnyBoard [14].

In a natural way, it has been proposed to separate control and data streams using different buses. That is shown in Figure 1.4b. Some examples of this configuration are PRISM developed at Boston University [8], and the University of Toronto's reconfigurable processor. Performance is still limited by the data and control buses bandwidth.

A third approach, showed in Figure 1.4c, is to have a circuit with a sea of reconfigurable gates in which a part is dedicated to perform the function of a conventional processor and the rest is devoted to implement algorithms through reconfigurable logic. It is intended to eliminate bandwidth restrictions. However, it is still at research level and no prototype is known to be already implemented [25].

#### 1.3 Our Approach

In implementing algorithms for FPGAs one must go from an algorithmic description to binary files which represent a design to configure one, or possibly more, FPGAs. Hardware description languages, although useful for digital design, are very low level languages for describing algorithms. Moreover, although much effort has been devoted to develop tools for the automatic synthesis of designs expressed in hardware description languages to FPGAs, there is a lack of techniques for synthesizing high level algorithmic descriptions to low level descriptions for FPGA computing.

In this research we present a design methodology to synthesize algorithms for FPGAs. We consider, on the one hand, the limitations of FPGAs, and on the other hand, the techniques developed to synthesize regular processor arrays [68]. We start from a dynamic programming algorithm expressed in a C\* program and we translate it to hardware description level in VHDL. Once we get hardware level descriptions we can use standard tools to synthesize a design for FPGAs.

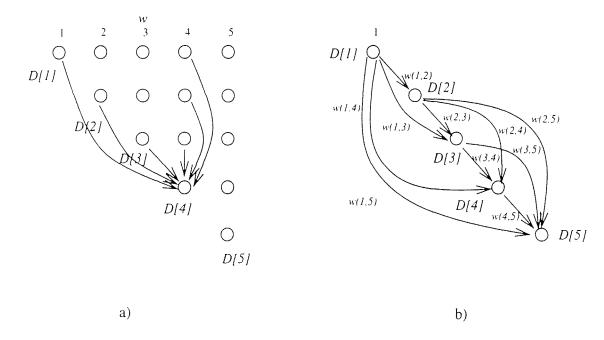

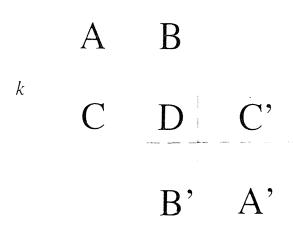

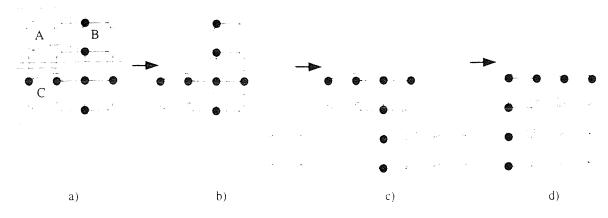

The process of synthesis to hardware description level is illustrated in Fig. 1.5. From nested loops containing data-parallel statements in C\* we obtain systems of recurrence equations (SRE) which are translated, when possible, into systems of uniform recurrence equations (SURE). Although there is no a general strategy to transform a SRE into a uniform shape, we explore how to address that problem. Decisions about variable alignment, operation serialization and interprocessor communication localization will be done through an interactive tool that applies transformations to the equations obtained.

Once we have generated a SURE we can explore different scheduling and allocation functions.

#### Imperative Programs

Data-Parallel Programs

Dataflow analysis

Systems of Recurrence Equations

Alignment, Serialization.

Localization

Systems of Uniform Recurrence Equations

Scheduling and Allocation

Space-Time Representation

Control Signal Generation

and I/O Mapping

#### Hardware Description Level

Figure 1.5: Translation C\* to hardware description level.

Linear transformations can be applied to SUREs to obtain a space-time representation from which we can derive the structure of a systolic array. The hardware level description of the array is found after generating the necessary control signals for the proper behavior of the array and after mapping the I/O channels onto the array.

#### 1.4 Summary of Major Contributions

Following is a summary of the important research contributions:

- 1. Determination of a class of algorithms for which FPGAs can be adequately used to obtain better performance than that which can be obtained in general-purpose computers. Current FPGA density prohibits their use for general purpose algorithms. The restrictions of FPGA technology are considered in determining the type of algorithms which can be benefited of being implemented in hardware.

- 2. A general design strategy to implement that class of algorithms through the data-parallel paradigm is proposed. As a first step, the C\* programming language is used as a high level description for the class of algorithms determined in step 1. Design strategies are proposed for implementing that class of algorithms for two target architectures: FPGA-based computing engine, and a general-purpose parallel computer.

- 3. Compilation tools to transform data-parallel programs in suitable form for hardware synthesis. A combination of automatic and manual techniques are provided for developing hardware |eve| descriptions of data-parallel programs.

- 4. A generic behavioral hardware description model is proposed which is based on reconfigurable hardware and is adequate to implement the class of algorithms determined in step 1.

- 5. All the previous parts are integrated to provide a general framework for the implementation of algorithms in reconfigurable hardware based on FPGAs. I will propose a general framework to the synthesis of algorithms for FPGA computing.

#### 1.5 Overview of the Thesis

The thesis is organized in 8 chapters. In chapter 2, we discuss dynamic programming problems and we present a classification of them. In chapter 3, we present a new approach to implement a

class of DP problems in a general-purpose multicomputer. In chapter 4 we introduce the concept of recurrence equations which are fundamental to understand the rest of the work. In chapter 5, we develop an algorithm to extract recurrence equations from C\* program fragments. Chapter 6 is devoted to discussing the uniformization process of recurrence equations and a tool to perform such a job is described. In chapter 7 we present an approach to generate hardware level descriptions from space-time representations. Finally, conclusions are drawn in Chapter 8.

### Chapter 2

# A Classification of Dynamic Programming Algorithms

#### 2.1 Introduction

Dynamic programming (DP) is a general problem solving strategy often applied to optimization problems. The theory of dynamic programming was originally introduced by Richard Bellman to solve mathematical problems arising from multistage decision processes [12]. Dynamic programming has found numerous applications in computer science such as: optimal parenthesization [39], line and curve detection [22], parsing of general context-free languages [21, 17], string matching [54, 55], handwritten symbol recognition [20]. Its application was particularly successful in speech recognition [69, 75, 62, 79], and in image processing and computer vision [61, 9]. These are also applications in which the running time is critical and in which parallel processing is required.

Many different approaches have been proposed to implement dynamic programming algorithms. Some of them have tried to obtain general strategies for deriving implementations of various problems. However, currently there is not a general strategy to implement dynamic programming. To understand the nature of DP problems we need to make some observations about their formulation.

In this chapter we explore general formulations of DP problems based on three type of classifications. In the first type we determine if the formulation involves just one subproblem, a fixed number of subproblems or a non-fixed number of subproblems. In the second aspect we will consider whether the recursive formulation is inherently sequential or can be decomposed to ignore sequentiality. In the third point of view, we will consider the dimensionality of the DP table as a clue to the complexity order of the problem.

In section 2.1 we will review the formulation of dynamic programming problems. We will consider the Principle of Optimality that all DP problems must obey. In section 2.2 we review the classification of DP problems and we will extend that classification considering important aspects of the formulations for its implementation. In section 2.3 we will present a set of problems that illustrate each of the classes we will consider. A discussion about implementation issues can be found in chapter 3.

#### 2.2 Dynamic Programming Formulations

Dynamic programming (DP) is a general problem-solving strategy often applied to optimization problems. The general formulation can be stated as follows: let

$$P^o: p^* = opt_{x \in X} q(x) \tag{2.1}$$

be an optimization problem where X is the solution set and q is a real valued function defined as the objective function. Sneidovich [77] showed that  $P^o$  will yield a dynamic programming optimality

equation if the solution set X is a subset of the Cartesian product of two sets,  $Y \times Z$ , leading to reformulate the problem in the following manner:

$$p^{\bullet} = opt_{(y,z) \in X} q(y,z), \qquad X \subset Y \times Z$$

(2.2)

Now, if we express X as the union of bundles  $\{y\} \times Z(y)$  where  $y \in Y$  and  $Z(y) \subset Z$ , i. e.  $X = \bigcup [y \times Z(y)]$ , we can reformulate Eq. (2.2) as follows:

$$p^{\bullet} = opt_{y \in Y} p(y) \tag{2.3}$$

where,

$$\forall y \in Y : p(y) = opt_{z \in Z(y)} q(y, z) \tag{2.4}$$

The decomposition of the original problem into two optimization problems is due to the *Principle of Optimality* [13], which states that an optimal sequence of decisions has the property that whatever the initial state and decision are, the remaining decisions must constitute an optimal decision sequence with regard to the state resulting from the first decision. An effort devoted to the rigorous mathematical framework and effective evaluation of DP problems can be found in [77].

Clearly, dynamic programming problems can be formulated using a recurrence relation involving a decision process. Dynamic programming decomposes a problem into a number of smaller subproblems, each of which is further decomposed until subproblems have trivial solutions. For example, a problem of size n may decompose into several problems of size n-1, each of which decomposes into several problems of size n-2, etc. This decomposition seems to lead to an exponential-time algorithm, which is indeed true for some problems, such as the traveling salesman problem. However, in many other problems there are only a polynomial number of distinct subproblems. Dynamic programming gains its efficiency by avoiding solving common subproblems many times. It keeps track of the solutions of subproblems in a table, and it performs table lookup whenever needed.

From the algorithmic design point of view, the development of a dynamic programming strategy has four steps: (1) characterize the structure of an optimal solution, (2) recursively define the value of an optimal solution, (3) compute the value of an optimal solution in a bottom-up fashion, and (4) construct an optimal solution from the computed information [24]. Once this is known, a two-step dynamic programming algorithm emerges: (1) construction of a table in a bottom-up fashion which contains solutions to smaller subproblems of the given problem (forward step), and (2) construction of a solution for the given problem (backward step). The big challenge in dynamic programming strategies is how to build the DP table.

Each entry of a DP table corresponds to a subproblem. Thus, the size of the table is the total number of subproblems including the problem itself. Because of the recurrent formulation, each entry of the table depends on one or several subproblems. Therefore, the order to fill the table may be chosen under the restriction of the table and the entry dependency. For sequential implementations there is an obvious algorithm which fills the table according to the entry dependency. To exploit parallel processing, we must examine the recurrence formulation.

#### 2.3 Classification of DP Algorithms

In this section we will unify the classifications done by Li and Wah [53] and Galil and Park [35].

Li and Wah classified DP problems according to the form of their functional equations and the nature of the recursion. That classification was first used to derive some systolic algorithms. Later on, Kumar [49] used the same classification to show practical implementations of problems belonging to each class.

In general, the solution to a DP problem is expressed as a minimum (or maximum) of possible alternative solutions. Each of these alternative solutions is constructed by composing one or more

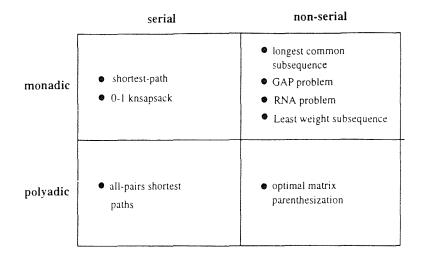

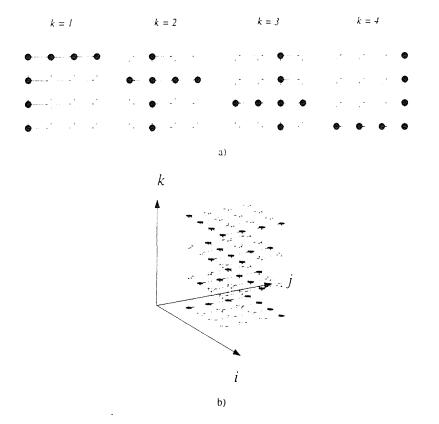

Figure 2.1: Dynamic programming problems classification and examples.

subproblems. A DP formulation is called *monadic* if its composition function involves only one recursive term; otherwise it is called *polyadic*. A DP formulation is *serial* if the subproblems can be grouped in levels, and the solution to any subproblem in a certain level can be found using subproblems that belong only in the immediately preceding levels. Otherwise it is *non-serial*. As shown in [53, 49] *monadic-serial* DP problems can be solved by a series of matrix-vector multiplications which is easy to parallelize. On the other hand, there is no general parallel formulation for *polyadic-serial* DP problems. In Figure 2.1 some example problems are presented according to their formulation.

Galil and Park [35] classified DP problems according the size of the table and the number of dependencies in a single problem. A dynamic programming problem is called a tD/eD problem if its table size is  $O(n^t)$  and a table entry depends on  $O(n^e)$  other entries. Although Galil and Park did not discuss the importance of the classification, the number of dependencies is of relevance to derive efficient implementations.

In Table 2.1 we present a number of DP algorithms and their characteristics according to the preceding discussion. We can see that problems with more than O(1) dependencies can be monadic or polyadic, serial or nonserial. We can make various observations of the characteristics of DP problems in considering them to derive efficient implementations.

As it will be evident in the next sections, the fact that a problem is serial or nonserial affects the way in which we build the DP table. In a serial problem, only the current and the previous level subproblems need to be stored. In a nonserial problem, solved subproblems on all previous levels are required. When we write an imperative program to fill the table of a nonserial problem, we need a scheduling policy.

Whether a problem is monadic or polyadic influences the way in which the solution of a specific problem is built (the second stage in the algorithmic point of view). Solutions of monadic problems are built in a serial fashion. Solutions of polyadic problems can be built by a divide-and-conquer strategy.

#### 2.4 Some Examples of DP Problems

In this section we will present some problems and we will discuss their formulations and classifications.

#### 2.4.1 The Shortest-Path Problem

The solution to the shortest-path problem was the original dynamic programming strategy proposed by Bellman [12]. It considers computing the minimum path between a source and a destination point

| Problem<br>Formulation                                                                                                                                                                                                                                          |              |           | Deps.    | T. Size  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|----------|----------|

| Shortest Path <sup>[24]</sup>                                                                                                                                                                                                                                   |              |           |          | 0 ( 3)   |

| $C_i^l = \min_{1 \le j \le n} \{ c_{ij}^l + C_j^{l+1} \}$                                                                                                                                                                                                       | monadic      | serial    | O(n)     | $O(n^2)$ |

| 0-1 Knapsack [49]                                                                                                                                                                                                                                               |              |           |          |          |

| $F[i,x] = \begin{cases} x \ge 0, i = 0 \to 0 \\ x < 0, i = 0 \to -\infty \\ 1 \le i \le n \to \max\{F[i-1,x], F[i-1,x-w_i] + p_i\} \end{cases}$ $Longest\ Common\ Subsequence^{[24]}$ $\begin{cases} i = 0 \lor j = 0 \to 0 \end{cases}$                        | monadic      | serial    | O(1)     | $O(n^2)$ |

| Longest Common Subsequence <sup>[24]</sup>                                                                                                                                                                                                                      |              |           |          |          |

| $F[i,j] = \begin{cases} i, j > 0 \land a_i = b_j \to & F[i-1, j-1] + 1\\ i, j > 0 \land a_i \neq b_j \to & \max\{F[i-1, j], \\ & F[i, j-1]\} \end{cases}$                                                                                                       | monadic      | nonserial | O(1)     | $O(n^2)$ |

| Edit Distance <sup>[24]</sup>                                                                                                                                                                                                                                   |              |           |          |          |

| $F[i,j] = \begin{cases} i = 0 \lor j = 0 \to 0 \\ i = 0 \land j > 0 \to D[0,j-1] + K_o \\ i > 0 \land j = 0 \to D[i-1,0] + K_a \\ i,j > 0 \to \min\{D[i-1,j-1] + d(t_i,r_j), \\ D[i,j-1] + K_o \\ D[i-1,j] + K_a \} \end{cases}$                                | monadic      | nonserial | O(1)     | $O(n^2)$ |

| $D[i,j] = \min \begin{cases} D[i-1,j-1] + s_{ij} \\ \min_{0 \le q < j} \{D[i,q] + w(q,j)\} \\ \min_{0 \le p < i} \{D[p,j] + w'(p,i)\} \end{cases}$                                                                                                              | monadic<br>- | nonserial | O(n)     | $O(n^2)$ |

| $RNA^{[76]}$ $D[i,j] = \min_{0 \le p < i  0 \le q < j} \{D[p,q] + w(p,q,i,j)\}$                                                                                                                                                                                 | monadic      | nonserial | $O(n^2)$ | $O(n^2)$ |

| Least Weight Subsequence <sup>[42]</sup> $D[j] = \min_{0 \le i < j} \{D[i] + w(i, j)\} \text{ for } 1 \le j \le n$                                                                                                                                              | monadic      | nonserial | O(n)     | O(n)     |

| $All \ Pairs \ Shortest \ Paths^{[24]}$ $d_{ij}^{(k)} = \begin{cases} k = 0 \to w_{ij} \\ k \ge 1 \to \min\{d_{ij}^{(k-1)}, d_{ik}^{(k-1)} + d_{kj}^{(k-1)}\} \end{cases}$                                                                                      | polyadic     | serial    | O(1)     | $O(n^3)$ |

| $ Optimal\ Matrix\ Parenthesization^{[24]} $ $ m(i,j) = \left\{ \begin{array}{ccc} 1 \leq i < j \leq n \rightarrow & \min\limits_{i \leq k < j} \{m(i,k) + \\ & m(k+1,j) + \\ & r_{i-1}r_kr_j \} \end{array} \right. $ $ j = i, 0 \leq i \leq n \rightarrow 0 $ | polyadic     | nonserial | O(n)     | $O(n^2)$ |

Table 2.1: A set of dynamic programming algorithms.

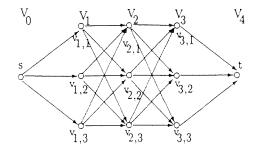

Figure 2.2: A multistage graph for the shortest-path problem.

where the path passes a number of stages, in each stage several possibilities exist as it is shown in Figure 2.2. Let G=(V,E) be a multistage graph in which V is the set of vertices and E is the set of edges.  $V=V_0\cup V_1\cup \cdots \cup V_N$ , where  $V_i,\ 0<=i< N$  is the set of nodes in stage  $i,\ V_0=\{s\}$  and  $V_N=\{t\}$ , and  $v_{ij}$  is the j'th node in  $V_i$ . We assume that there exist exactly m nodes in each stage other than 0 and N. The cost of a path from the source node, s, to sink node, t, is the sum of costs on the edges of the path. Let P be the set of all possible paths from s to t. A path  $p\in P$  is of the form  $s-v_{1j_1}-v_{2j_2}-\ldots-v_{n-1j_{n-1}}-t$ . If the cost of edge  $(v_{ij_i},v_{i+1,j_{i+1}})$  is  $g_i(v_{ij_i},v_{i+1j_{i+1}})$  the minimum-cost path from s to t is:

$$\min_{p \in P} f(p) = \min_{p \in P} \sum_{i=0}^{N-1} g_i(v_{ij_i}, v_{i+1j_{i+1}})$$

(2.5)

Each term in optimization problems of this form shares one variable with its predecessor term and another one with its successor term. This problem has a serial structure, and, consequently, is called a serial optimization problem. Many practical problems can be formulated in this way: traffic-control, circuit-design, fluid-flow and scheduling.

We can reformulate the problem as follows. Let us assume for simplicity that every stage consists of exactly m nodes. Let  $c^k(j), 0 \le k \le N, 1 \le j < m$ , be the minimum cost of going from node j in stage k to the sink node, t. We can group the  $c^k(j)$  values into a vector of the following form

$$C^{k} = [c^{k}(0), c^{k}(1), ..., c^{k}(m-1)]^{T}$$

(2.6)

Let  $M^k = g_k(i, j)$  be the cost of going from node i, in stage k, to node j in stage k+1,  $1 \le k < N$ .  $M^k$  is a  $m \times m$  matrix. It can be seen that

$$C^{k} = M^{k} * C^{k+1}, 1 \le k < N \tag{2.7}$$

which is a matrix-vector multiplication where products can be interpreted as additions and additions as minimum selection operations. This formulation induces a sequence of N-1 matrix-vector-style multiplications. Then, the solution of the problem can be easily computed from the dot product

$$C^{0} \cdot C^{1} = [g_{0}(0), g_{0}(1), ..., g_{0}(m-1)]^{T} \cdot C^{1}$$

(2.8)

where,  $g_0(j)$  is the cost of going from source node, s, to node j in stage 1. Equations 2.7 and 2.8 provide us a recurrent formulation for this problem. Since the composition function involves only one recursive term, this problem is monadic. For obvious reasons it is serial. It presents a fixed number of dependencies and its table is of size  $N \times m$ .

#### 2.4.2 The Knapsack Problem

This is a classical problem used to illustrate DP algorithmic formulations. It has received great attention for many researchers looking for efficient implementations. See [7] for a novel approach.

Suppose that m types of objects are being considered for inclusion in a knapsack of capacity c. For  $i = 1, 2, \dots, m$ , let  $p_i$  be the *profit* and  $w_i$  the weight of the *i*-th type of object, where  $w_i$ ,  $p_i$ , and c are all positive integer. The knapsack problem is to choose a collection of objects in such a way that the total profit without exceeding the capacity is maximized, i.e.,

$$\max \left\{ \sum_{i=1}^{m} p_i z_i : \sum_{i=1}^{m} w_i z_i \le c, z_i \in \mathbb{N}, i = 1, 2, \cdots, m \right\}$$

(2.9)

where  $z_i$  is the number of *i*-th type objects included in the knapsack. The problem, as specified above is often called the *unbounded knapsack problem*, since the only constraint on the solution (other than the capacity constraint) is that it is non-negative. There are many variations of the problem, such as the *bounded knapsack problem* (here, additional constraints of the form  $z_i \leq b_i$  must be satisfied), the 0/1 knapsack problem (a particular case of the bounded problem, where  $b_i = 1$ : there is exactly one copy of each type of object), the subset sum problem (a 0/1 problem with  $w_i = p_i$ ), the change making problem, etc. They arise in different application domains, and are all NP-complete.

Let us define the function f(j, k) which denotes the value of an optimal solution of the subproblem where only the first k objects are considered, and only a capacity of j is available. It is well known that the computation of f(i, j) is specified recursively as follows:

$$f(i,j) = \begin{cases} 0 & \text{if } j = 0 \text{ or } k = 0\\ f(j,k-1) & \text{if } k > 0 \text{ and } j < w_k\\ f(j,k-1) \oplus (p_k + f(j-w_k,k-\beta)) & \text{if } k > 0 \text{ and } j \ge w_k \end{cases}$$

(2.10)

where f(c,m) is the solution to the problem. The different variations of the knapsack problem merely correspond to different choices of the operator  $\oplus$  and the constant  $\beta$  in Eq. 2.10: in the unbounded knapsack problem,  $\oplus$  is max, and  $\beta = 0$ ; in the 0/1 and subset-sum problems,  $\oplus$  is max and  $\beta = 1$ ; in the change making problem  $\oplus$  is min and  $\beta = 0$ .

An elegant, memory efficient implementation for the problem can be found in [43]. It is computed in time O(c+m) time and c space (only the last column needs to be saved, not the entire table). Because of the dynamic dependencies existing in the knapsack problem, this problem has been heavily studied. One instance of this problem can be observed in Figure 2.3. This is another monadic-serial algorithm whose table is  $m^2$  having constant non-fixed dependencies.

#### 2.4.3 Longest Common Subsequence

The longest-common subsequence problem belongs to a class of widely studied problems related to string-matching [76]. Finding the longest-common subsequence of two strings can be stated as follows: a subsequence  $z=\langle z_1,z_2,\cdots,z_k\rangle$  is a subsequence of  $x=\langle x_1,x_2,\cdots,x_n\rangle$  if there exists a strictly increasing sequence  $\langle i_1,i_2,\cdots,i_k\rangle$  of indices of X such that for all  $j=1,2,\cdots,k$ , we have  $x_{i_j}=z_j$ . A common subsequence of A and B is a sequence Z that is a subsequence of both A and B. For example the sequence  $\langle B,C,B\rangle$  is a common subsequence of  $\langle B,D,C,A,B,A\rangle$  and  $\langle A,B,C,B,D,A,B\rangle$ . Given two sequences  $A=\langle a_1,a_2,\cdots,a_n\rangle$  and  $B=\langle b_1,b_2,\cdots,b_m\rangle$  we wish to find a maximum-length common subsequence of A and B. For the previous example the longest common subsequence is  $\langle B,C,B,A\rangle$ .

The dynamic programming formulation of the problem computes F[i,j]  $(0 \le i \le n, 0 \le j < m)$ , where F[i,j] denotes the longest common subsequence of the first i elements of A and the first j elements of B, and it is defined by the following recurrence equation.

Figure 2.3: Dependencies of the knapsack problem.

|   |   | В | D | С | A | В | A |

|---|---|---|---|---|---|---|---|

|   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| A | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| В | 0 | 1 | 1 | 1 | 1 | 2 | 2 |

| C | 0 | 1 | 1 | 2 | 2 | 2 | 2 |

| В | 0 | 1 | 1 | 2 | 2 | 3 | 3 |

| D | 0 | 1 | 2 | 2 | 2 | 3 | 3 |

| A | 0 | 1 | 2 | 2 | 3 | 3 | 4 |

| В | 0 | 1 | 2 | 2 | 3 | 4 | 4 |

Figure 2.4: An example of the longest common subsequence problem.

$$F[i,j] = \begin{cases} i = 0 \lor j = 0 \to 0 \\ i,j > 0 \land a_i = b_j \to F[i-1,j-1] + 1 \\ i,j > 0 \land a_i \neq b_j \to \max\{F[i-1,j], F[i,j-1]\} \end{cases}$$

(2.11)

The goal is to find F[n,m]. One example of the computation of the table for a simple problem is presented in Figure 2.4. Equation 2.11 presents a monadic formulation since the composition function involves only one term. It is nonserial due to the case when both symbols match. Clearly, the table is  $n \times m$  and the dependencies are fixed.

#### 2.4.4 Edit Distance

The edit distance problem is another member of the string matching class. In this problem instead of computing the longest match, it calculates the cost of transforming one string to another one.

Let  $T=(t_1,t_2,\ldots,t_i,\ldots,t_n)$  and  $R=(r_1,r_2,\ldots,r_j,\ldots,r_m)$  be two strings to compare. We are interested in the cost of transforming string R to string T. We can apply successive comparisons

Figure 2.5: Dependencies in the Edit Distance Problem.

between elements of R and elements of T. When a mismatch occurs, we must consider the possibility of replacing a character of T for one of R, of inserting a character of T, or deleting a character of R. This problem can be well defined by the following recurrence relation stating a dynamic programming problem:

$$D(i,j) = \min \begin{cases} D(i-1,j-1) + d(t_i,r_j) \\ D(i-1,j) + K_a \\ D(i,j-1) + K_o \end{cases}$$

(2.12)

with the initial conditions:

$$\begin{array}{lcl} D(0,0) & = & 0 \\ D(i,0) & = & D(i-1,0) + K_a & \text{for } 1 \le i \le n \\ D(0,j) & = & D(0,j-1) + K_o & \text{for } 1 \le j \le m \end{array}$$

where  $d(t_i, r_j)$  represents the cost of replacing  $r_j$  by  $t_i$ ,  $K_a$  the cost of adding  $t_i$ , and  $K_o$  the cost of omitting  $r_j$ . Note that in this formulation, the costs of insertion and suppression are constant, independent from the specific characters. In a typical application, like spelling correction, this calculation has to be repeated a lot of times since the same test string must be compared to many reference strings (a full dictionary for example). Therefore the amount of computation can be very large and prohibits the use of a conventional computer. In Figure 2.5, the dependencies between elements in the table are shown. For the same reasons as the previous subsection problem, this is monadic-nonserial with constant dependencies in a  $n^2$  table.

#### 2.4.5 Gap Problem

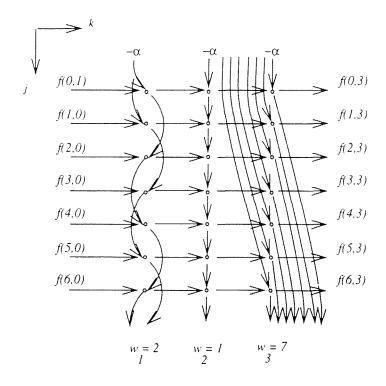

The gap problem is a generalization of the edit distance problem when costs of insertions and suppressions are variable and when allowing gaps of insertions and deletions. It can be stated as follows. Given w, w',  $s_{ij}$ , and D[0,0], compute

$$D[i,j] = \min \begin{cases} D[i-1,j-1] + s_{ij} \\ \min_{0 \le q < j} \{D[i,q] + w(q,j)\} & \text{for } 0 \le i \le m \\ \min_{0 \le p < i} \{D[p,j] + w'(p,i)\} \end{cases}$$

(2.13)

Figure 2.6: Dependencies of the gap problem.

The gap problem arises in molecular biology, geology, and speech recognition [33]. From Figure 2.6 we can observe that this problem describes a two dimensional table where a single subproblem depends on its northwest neighbor and all previous problems along the same row and the same column.

It is easy to see that the computational effort to solve the entry (i,j) takes O(i+j) time. Therefore, a sequential algorithm to compute the problem takes  $O(n^3)$  time. It can proceed along rows, columns, or diagonals. It is a monadic problem. It is nonserial since Equation 2.13 involves several subproblems on the right hand side. For the same reason, its dependencies are nonconstant (O(n)). It has a  $n^2$  table.

#### 2.4.6 RNA Problem

The RNA problem is the generalization of the two string matching problem. Here the cost function allows insertions, suppressions, and loops with variable cost. Given w and D[i,0] and D[0,j] for  $0 \le i,j \le n$ , compute

$$D[i,j] = \min_{0 \le p < i} \{D[p,q] + w(p,q,i,j)\} \quad \text{for } 1 \le i,j \le n$$

(2.14)

This problem has been used to compute the secondary structure of RNA without multiple loops. As can be seen from Figure 2.7, each subproblem depends on all the north-west subproblems. Therefore, the computational effort to solve the entry (i,j) takes  $O(i \times j)$  time. Given that we have a two-dimensional table, a sequential algorithm to compute the problem takes  $O(n^4)$  time. In a similar way to the Gap Problem, the sequential algorithm can proceed along rows, columns, or diagonals.

The RNA problem refers a monadic-nonserial problem in which the dependencies are variable  $(O(n^2))$  and describes a two dimensional table.

#### 2.4.7 Least Weight Subsequence

Given a real-valued function w and D[0], compute

$$D[j] = \min_{0 \le i \le j} \{ D[i] + w(i,j) \} \quad \text{for} \quad 1 \le j \le n$$

(2.15)

Figure 2.7: Dependencies of the RNA problem.

This problem was called the least weight subsequence problem by Hirschberg and Larmore [42]. Its applications include an optimum paragraph formation problem and the problem of finding a minimum height B-tree.

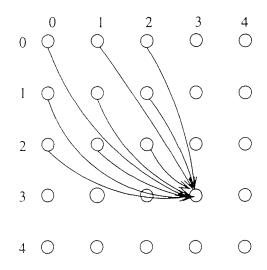

The subproblem dependencies can be visualized in the Figure 2.8. In Figure 2.8a a two dimensional view of the problem can be observed. An upper triangular table is constructed where the D[i]'s values are produced along the main diagonal. Also, a graph representation can be generated for this problem. A directed graph G is built from recurrence 2.15. The vertices of the graph are  $0,1,\cdots,n$ . The edges (i,j) for all i < j, and edge (i,j) has cost w(i,j). If f(j) is the shortest path from 0 to j in graph G, then, it can be shown that D[i] = f(i). The directed graph view can be observed in Figure 2.8b. It can be shown that the problem stated by recurrence 2.15 is similar to the problem of finding the shortest paths in G from 0 to all vertices.

Recurrence 2.15 presents a monadic-nonserial problem with a variable number of dependencies in a one-dimensional table.

#### 2.4.8 All-Pairs Shortest Paths

The all-pairs shortest paths problem belongs to a more general class of problems known as algebraic path problems. Some additional examples of problems belonging to this class are the transitive closure problem, the matrix inversion problem and the generation of regular languages. All problems belonging to this class share a common formulation. Variation among them depends on the semi-ring in which a specific problem is defined.

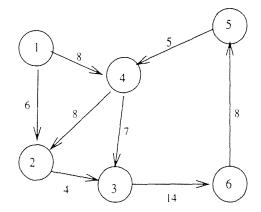

We will review here only the all-pairs shortest path problem. We should be aware that all related problems share the same formulation. Given a weighted, directed graph  $G = \langle V, E \rangle$  with weight function  $w: E \to R$  mapping edges to real valued weights, we are interested in finding a shortest path from u to v for every pair of vertices u and v. An example of this problem can be observed in Figure 2.9.

The well known Floyd's algorithm to solve this problem is based on the following dynamic programming formulation. Let  $d_{ij}^{(k)}$  be the weight of a shortest path from vertex i to vertex j with all intermediate vertices in the set  $\{1, 2, \cdots, k\}$ .  $d_{ij}^{(k)}$  can be computed from the following recurrence equation.

$$d_{ij}^{(k)} = \begin{cases} k = 0 \to w_{ij} \\ k \ge 1 \to \min\{d_{ij}^{(k-1)}, d_{ik}^{(k-1)} + d_{kj}^{(k-1)}\} \end{cases}$$

(2.16)

Figure 2.8: The least weight subsequence problem.

The matrix  $D^{(n)} = d_{ij}^{(n)}$  represents the solution to the problem, where n is the number of vertices in the graph. This formulation belongs to the polyadic-serial class because its composition functions involves more than one recursive term, but they are only on the previous level subproblems. It exhibits a  $n^3$  table involving constant dependencies.

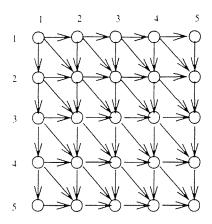

#### 2.4.9 Optimal Matrix Parenthesization

Consider the evaluation of the product of n matrices  $A_1, A_2, \dots, A_n$ , where each  $A_i$  is a matrix with  $r_{i-1}$  rows and  $r_i$  columns. The order in which the matrices are multiplied together can have a significant effect on the total number of operations required to evaluate the product. Trying all possible orderings in which to evaluate the product of n matrices, so as to minimize the number of operations, is an exponential process which is impractical when n is moderately large. However, dynamic programming provides an  $O(n^3)$  sequential algorithm. Let m(i,j) be the cost of multiplying the matrices  $A_i, A_{i+1}, \dots, A_j$ . The dynamic programming paradigm constructs the solution to this problem based on the solutions to its subproblems. To compute m(i,j) computes the minimum value of all possible parenthesization between  $A_i$  and  $A_j$ . This approach gives rise to the following recurrence equation for the parenthesization problem:

$$m(i,j) = \begin{cases} 1 \le i < j \le n \to \min_{\substack{i \le k < j \\ j = i, 0 \le i \le n \to 0}} \{ m(i,k) + m(k+1,j) + r_{i-1}r_k r_j \} \\ j = i, 0 \le i \le n \to 0 \end{cases}$$

(2.17)

Given Eq. (2.17) the problem reduces to finding the value for m(1,n). This problem has been heavily studied. One important aspect of this problem is the nature of interactions between subproblems for solving an specific problem. As can be seen in Figure 5, in order to solve a problem corresponding to the table's entry (i,j) we require all the problems in previous columns to be on the same row and all the problems in down rows to be in the same column. Furthermore, considering Eq. (2.17) they are required to be in a pairwise fashion as shown in Figure 2.10.

$$A = \begin{bmatrix} 0 & 6 & \infty & 8 & \infty & \infty \\ \infty & 0 & 4 & \infty & \infty & \infty \\ \infty & \infty & 0 & \infty & \infty & 14 \\ \infty & 8 & 7 & 0 & \infty & \infty \\ \infty & \infty & \infty & 5 & 0 & \infty \\ \infty & \infty & \infty & \infty & 8 & 0 \end{bmatrix} \qquad A^{+} = \begin{bmatrix} 0 & 6 & 10 & 8 & 32 & 24 \\ \infty & 0 & 4 & 31 & 26 & 18 \\ \infty & 35 & 0 & 27 & 22 & 14 \\ \infty & 8 & 7 & 0 & 29 & 21 \\ \infty & 13 & 12 & 5 & 0 & 26 \\ \infty & 21 & 20 & 13 & 8 & 0 \end{bmatrix}$$

Figure 2.9: An example of the all-pairs shortest paths problem.

#### 2.5 Dynamic Programming Remarks

From the set of examples we have presented we can see that dynamic programming is basically a decomposition strategy. The general idea is to solve simple subproblems and progressively solve larger problems composed of already solved problems. The computational effort to solve a single subproblem is low, however, considering the dependencies each subproblem has, it seems to lead to inherently sequential algorithms. Other approaches have been followed to overcome with the sequential nature of DP algorithms. Parallel processing and hardware implementation are alternatives. Particularly, hardware level implementation have been followed for several reasons. First, as in the string matching problem, it is common to solve many instances of the problem which requires fast execution. Second, the arithmetic involved in several problems is not so complex. From the examples we have reviewed we can observe that in many cases integer arithmetic with low precision is enough. Finally, being able to re-organize the recursive formulations in such a way that we obtain local and regular dependencies we can implement them in FPGA circuitry. Techniques to achieve that will be discussed in chapter 5.

#### 2.6 Conclusions

We have presented the general formulation of dynamic programming algorithms. We showed how the decomposition of a problem into subproblems can lead to a DP formulation. We reviewed the classifications of DP problems. From a set of examples, we have made some observations about efficient implementations of DP formulations. It has been believed that dynamic programming is adequate for sequential computers and not appropriate for parallel machines. In the next chapter we will show how to exploit parallelism in dynamic programming formulations.

Figure 2.10: An instance of the optimal matrix parenthesization problem.

### Chapter 3

# Data-Parallel Dynamic Programming