Computer Science Department

### Implementation of Cryptographic Algorithms for High-speed and Constrained Devices

A dissertation submitted by

### Jose Abraham Bernal Gutierrez

For the degree of

### Doctor in Computer Science

Advisors:

#### Dr. Francisco Rodr guez Henr quez Dr. Cuauhtemoc Mancillas Lopez

Mexico City

April 2023

# Centro de Investigación y de Estudios Avanzados del IPN

Departamento de Computación

### Implementacion de algoritmos criptogra cos para dispositivos de alta velocidad y dispositivos restringidos

Tesis que presenta

## Jose Abraham Bernal Gutierrez

para obtener el grado de

### Doctor en Ciencias en Computacion

Directores de tesis:

#### Dr. Francisco Rodr guez Henr quez Dr. Cuauhtemoc Mancillas Lopez

Ciudad de México

Abril 2023

# Acknowledgments

Agradezco al Consejo de Ciencia y Tecnología (CONACYT) el apoyo brindado para realizar mis estudios y así alcanzar el grado de doctor en ciencias en computación.

También agradezco al Centro de Investigación y de Estudios Avanzados del Instituto Politécnico Nacional (Cinvestav IPN) la oportunidad de ingresar al programa de doctorado en el departamento de computación.

## Resumen

Esta tesis presenta los trabajos desarrollados centrados en la criptografía simétrica y la criptografía de clave pública. Hoy en día, el despliegue de muchos dispositivos con diferentes capacidades da lugar a entornos heterogéneos. Estos entornos deben garantizar la seguridad de los datos recogidos y procesados por los dispositivos en el entorno desplegado. Para proteger los dispositivos en función de sus capacidades, implementamos enfoques criptográficos en distintos proyectos que parten de la crip-

sobre dos enfoques matemáticos, el primero basado en el esquema RSA con RNS y la implementación general del módulo multiplicador base para mejorar la velocidad y explotar los DSPs disponibles en FPGAs con un enfoque en un multiplicador de propósito general que acepta cualquier número primo de 512 bits. Esta propuesta presenta algunos problemas debido a la generalización de la implementación. Puede utilizar muchos dispositivos si se desea alcanzar altas velocidades; por otro lado, puede utilizar menos y lograr una velocidad menor. El segundo multiplicador utiliza los enteros para realizar las multiplicaciones necesarias en un esquema de criptografía de curvas elípticas ECC centrado en la curva ECC25519; esta segunda propuesta utiliza tres algoritmos de multiplicación el primero es RNS, el método de multiplicación Karatsuba, y la multiplicación del método de la escuela. Comparamos las tres propuestas y presentamos resultados interesantes cuando logramos paralelizar simultáneamente algunas operaciones y procesar múltiples resultados intermedios con arquitecturas dedicadas para conseguir alta velocidad con bajo consumo de recursos.

## Abstract

This thesis presents the studies that we have developed focused on symmetric cryptography and public-key cryptography. Today, deploying many devices with different capabilities gives rise to heterogeneous environments. These environments must ensure the security of the data harvested and processed by the devices in the deployed environment. To protect the data stored and harvested by the devices, we implement cryptographic approaches into different focuses emanating from symmetric cryptography and public-key cryptography. The scope of this thesis consists of implementing both methods into devices with constrained resources such as memory, speed, and power and, therefore, into high-speed devices like FPGAs.

At the beginning of this thesis work, we present symmetric cryptography implementations. Some of the architectures described participated in the NIST LWC contest in standardizing Lightweight cryptography for constrained devices. Therefore, we made some implementations of LWC algorithms on hardware with a constrained focus on FPGAs and the architectures we proposed based on their algorithms. Some developed architectures and implementations were ranked among the first twenty places in a benchmarking performed by George Mason University. Finally, we present a software implementation of the Speedy algorithm, designed for hardware performance, but in software has a poor performance. This implementation uses a technique named "bitslice" which consists of rearranging the data bits to be processed as fast as possible, improving the speed and performance against traditional software implementations, and achieving an acceptable performance on microcontrollers like the ARM family, which has constrained resources and a small amount of memory available compare with conventional microprocessors.

In the remaining chapters, we work on public-key cryptography and propose two arithmetic multipliers for use in public-key cryptography on two mathematical approaches, the first based on the RSA scheme with RNS and the general implementation of the base multiplier module to improve the speed and exploit the digital signal processors (DSPs) available in FPGAs with a focus on a general purpose multiplier which accepts arbitrary 512 bits prime number. This approach has some issues due to the generalization of the implementation. It can use many devices if achieving high speeds is desired; on the other hand, it can use fewer and achieves a lower rate. The second multiplier uses the integers to perform the multiplications needed into a scheme of elliptic curve cryptography ECC focused on the curve ECC25519; this second proposal uses three multiplication algorithms: Residue Numeric system (RNS), the Karatsuba multiplication method, and the schoolbook multiplication. We compared the three proposals and presented exciting results when we could simultaneously parallelize some operations and process multiple intermediate results with dedicated architectures to achieve high speed with low resource consumption.

# Contents

| 1 | Intr | ntroduction                           |   |  |  |  |  |

|---|------|---------------------------------------|---|--|--|--|--|

|   | 1.1  | Motivation                            | 4 |  |  |  |  |

|   | 1.2  | Problem statement                     | 4 |  |  |  |  |

|   | 1.3  | Objectives                            | 5 |  |  |  |  |

|   | 1.4  | State-of-the-art                      | 6 |  |  |  |  |

|   |      | 1.4.1 Security on constrained devices | 8 |  |  |  |  |

|   |      | 1.4.2 Security on high-speed devices  | 1 |  |  |  |  |

|   | 1.5  | Summary                               | 2 |  |  |  |  |

13

### I Theoretical Background

| 2 | 2 Preliminaries |                                |    |  |  |

|---|-----------------|--------------------------------|----|--|--|

|   | 2.1             | Mathematical Background        | 15 |  |  |

|   | 2.2             | Algebra                        | 15 |  |  |

|   |                 | 2.2.1 Groups                   | 16 |  |  |

|   |                 | 2.2.2 Rings                    | 16 |  |  |

|   |                 | 2.2.3 Fields                   | 17 |  |  |

|   |                 | 2.2.4 Extension of fields      | 17 |  |  |

|   | 2.3             | Integer arithmetic operations  | 18 |  |  |

|   |                 | 2.3.1 Addition and Subtraction | 20 |  |  |

|   |                 | 2.3.2 Multiplication           | 20 |  |  |

|   |                 | 2.3.3 Modular reduction        | 22 |  |  |

|   | 2.4             | Greatest Common Divisor (GCD)  | 24 |  |  |

|   | 2.5             | Chinese Residue Theorem CRT    | 25 |  |  |

|   | 2.6             | Summary                        | 26 |  |  |

| 3 | Cry  | ptogra   | phy                                                                                        | 27 |

|---|------|----------|--------------------------------------------------------------------------------------------|----|

|   | 3.1  | Advan    | ced Encryption Standard (AES)                                                              | 28 |

|   |      | 3.1.1    | Byte Substitution layer                                                                    | 32 |

|   |      | 3.1.2    | ShiftRows                                                                                  | 32 |

|   |      | 3.1.3    | MixColumns                                                                                 | 34 |

|   |      | 3.1.4    | Add Round Key                                                                              | 34 |

|   |      | 3.1.5    | Key Schedule                                                                               | 35 |

|   |      | 3.1.6    | AES 128-bit Key schedule                                                                   | 35 |

|   | 3.2  | Block    | Cipher Modes of Operation                                                                  | 36 |

|   |      | 3.2.1    | Electronic Codebook (ECB)                                                                  | 36 |

|   |      | 3.2.2    | Cipher Block Chaining Mode (CBC)                                                           | 37 |

|   |      | 3.2.3    | Counter Mode (CTR) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 39 |

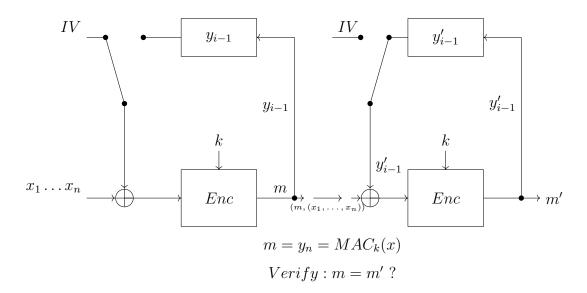

|   | 3.3  | Messag   | ge Authentication Codes (MACs)                                                             | 40 |

|   |      | 3.3.1    | HMAC                                                                                       | 41 |

|   |      | 3.3.2    | MAC from block ciphers                                                                     | 43 |

|   |      | 3.3.3    | MAC Verification                                                                           | 44 |

|   | 3.4  | Hash I   | Functions                                                                                  | 44 |

|   | 3.5  | Lightw   | reight Cryptography                                                                        | 44 |

|   |      | 3.5.1    | Performance                                                                                | 45 |

|   |      | 3.5.2    | Lightweight primitives                                                                     | 46 |

|   |      | 3.5.3    | Lightweight Block ciphers                                                                  | 46 |

|   |      | 3.5.4    | Lightweight MACs                                                                           | 46 |

|   | 3.6  | Auther   | nticated encryption with associated data                                                   | 47 |

|   | 3.7  | Hardw    | are API for Lightweight Cryptography                                                       | 48 |

|   | 3.8  | Public   | Key Cryptography                                                                           | 52 |

|   | 3.9  | RSA .    |                                                                                            | 53 |

|   |      | 3.9.1    | RSA encryption scheme                                                                      | 54 |

|   |      | 3.9.2    | RSA signature scheme                                                                       | 55 |

|   | 3.10 | Elliptie | c curve scheme                                                                             | 56 |

|   |      | 3.10.1   | Groups                                                                                     | 56 |

|   |      | 3.10.2   | Generalization of discrete logarithm problem                                               | 57 |

|   |      | 3.10.3   | Elliptic curve groups                                                                      | 57 |

|   |      | 3.10.4   | Key generation in elliptic curves                                                          | 58 |

|   |      | 3.10.5   | Encryption scheme with elliptic curves                                                     | 58 |

|   | 3.11 | Summa    | ary                                                                                        | 59 |

|   |      |          |                                                                                            |    |

5.3.8

5.5

| 4 | Fiel | d Prog  | grammable Gate Array (FPGA) and Advance RISC Ma-                                                                                          |

|---|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

|   | chir | ne (AR  | M) technologies 61                                                                                                                        |

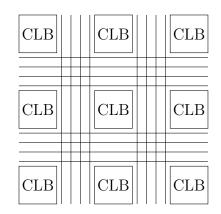

|   | 4.1  | Field I | Programmable Gate Arrays (FPGAs)                                                                                                          |

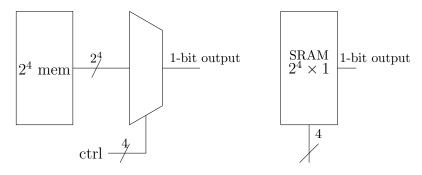

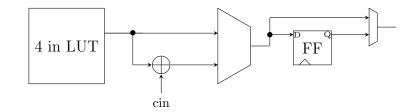

|   |      | 4.1.1   | Logic elements                                                                                                                            |

|   | 4.2  | Digita  | l Signal Processor (DSP) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 67$                                       |

|   |      | 4.2.1   | DSP48E2                                                                                                                                   |

|   |      | 4.2.2   | Xilinx FPGA Families                                                                                                                      |

|   | 4.3  |         | ecture of Xilinx 7 family                                                                                                                 |

|   |      | 4.3.1   | Configurable Logic Block (CLB)                                                                                                            |

|   |      | 4.3.2   | Look-Up Table (LUT)                                                                                                                       |

|   | 4.4  | Advan   | $ce RISC Machine (ARM) \dots \dots$ |

|   |      | 4.4.1   | Register Set                                                                                                                              |

|   | 4.5  |         | croelectronics                                                                                                                            |

|   |      | 4.5.1   | Memory protection unit                                                                                                                    |

|   |      | 4.5.2   | General-purpose I/O (GPIO                                                                                                                 |

|   |      | 4.5.3   | Direct memory access (DMA) 88                                                                                                             |

|   |      | 4.5.4   | Random number generator (RNG) 89                                                                                                          |

|   |      | 4.5.5   | AES in hardware                                                                                                                           |

|   |      |         |                                                                                                                                           |

| П | S    | ymme    | etric Key Cryptography 93                                                                                                                 |

| 5 | Liak | ntwoial | nt authenticated encryption with associated data in hard-                                                                                 |

| J | war  | 0       | 95                                                                                                                                        |

|   | 5.1  |         | nticated Encryption with Associated Data                                                                                                  |

|   | 5.2  |         | LWC Interface                                                                                                                             |

|   | 5.3  |         | nented Authenticated Ciphers                                                                                                              |

|   | 0.0  | 5.3.1   | Preliminaries                                                                                                                             |

|   |      | 5.3.2   | Hardware design principles                                                                                                                |

|   |      | 5.3.3   | LOTUS and LOCUS                                                                                                                           |

|   |      | 5.3.4   | LOTUS                                                                                                                                     |

|   |      | 5.3.5   | LOCUS                                                                                                                                     |

|   |      | 5.3.6   | ESTATE                                                                                                                                    |

|   |      | 5.3.7   | COMET                                                                                                                                     |

137

| 6 | Spe | edy Bl  | ock cipher on ARM with Bitslice            | 125 |

|---|-----|---------|--------------------------------------------|-----|

|   | 6.1 | Speedy  | y block cipher                             | 125 |

|   |     | 6.1.1   | Speedy S-Box                               | 127 |

|   |     | 6.1.2   | Speedy specification                       | 128 |

|   |     | 6.1.3   | Round function                             | 129 |

|   |     | 6.1.4   | Key schedule                               | 130 |

|   | 6.2 | Bitslic | ing                                        | 130 |

|   |     | 6.2.1   | Substitution Box (SB)                      | 131 |

|   |     | 6.2.2   | Shift Columns (SC)                         | 132 |

|   |     | 6.2.3   | MixColumns (MC)                            | 132 |

|   |     | 6.2.4   | AddRoundKey (AR) and AddRoundConstant (AC) | 133 |

|   | 6.3 | Result  | S                                          | 133 |

|   |     | 6.3.1   | Differential Attack                        | 135 |

#### III Public Key Cryptography

| 7 |              | )<br>SP-ba<br>tiplier | ased FPGA design and implementation of a fast RNS<br>139                                                                               |

|---|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|   | 7.1          | •                     | ontributions                                                                                                                           |

|   | $7.1 \\ 7.2$ |                       |                                                                                                                                        |

|   | 1.2          |                       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                   |

|   |              | 7.2.1                 | Notation                                                                                                                               |

|   |              | 7.2.2                 | Montgomery reduction                                                                                                                   |

|   |              | 7.2.3                 | Residue Number System and Modular Arithmetic 143                                                                                       |

|   |              | 7.2.4                 | RNS Montgomery modular reduction                                                                                                       |

|   |              | 7.2.5                 | FPGA and DSP technology 149                                                                                                            |

|   | 7.3          | Relate                | d works                                                                                                                                |

|   | 7.4          | Design                | of a DSP48 -based architecture for a field multiplier 153                                                                              |

|   |              | 7.4.1                 | Basic RNS multiplier with reduction                                                                                                    |

|   |              | 7.4.2                 | Multiplier array $MulDM$                                                                                                               |

|   |              | 7.4.3                 | RNS addition with reduction                                                                                                            |

|   |              | 7.4.4                 | Addition tree                                                                                                                          |

|   | 7.5          | Impler                | nentation $\ldots \ldots 161$ |

|   |              | 7.5.1                 | Implementation of the modular reduction Algorithm 19 162                                                                               |

|   |              | 7.5.2                 | Montgomery Implementation                                                                                                              |

|   | 7.6          | Result                | s                                                                                                                                      |

|   |              | 7.6.1                 | RNS word multiplier with reduction                                                                                                     |

|   |              | 7.6.2                 | Discussion and comparison                                                                                                              |

| 8 | Har | dware accelerator for the elliptic curve ECC25519 | 169 |

|---|-----|---------------------------------------------------|-----|

|   | 8.1 | Karatsuba Proposal                                | 170 |

|   | 8.2 | Schoolbook proposal                               | 176 |

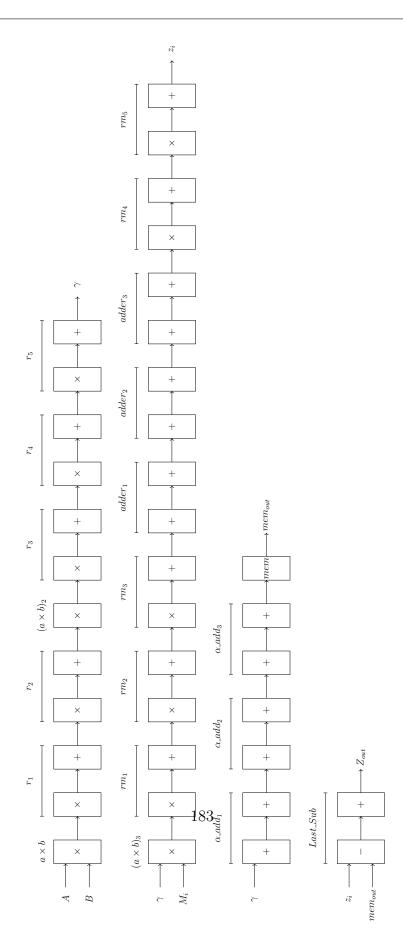

|   | 8.3 | RNS                                               | 181 |

|   | 8.4 | Results                                           | 184 |

|   | 8.5 | Summary                                           | 187 |

#### IV Summary

#### 189 101

| 9  | Con  | clusions                                                             | 191  |

|----|------|----------------------------------------------------------------------|------|

|    | 9.1  | Lightweight authenticated encryption with associated data $\ldots$ . | 191  |

|    | 9.2  | Speedy Block cipher on ARM-M4 with Bitslice                          | 191  |

|    | 9.3  | A DSP-based FPGA design and implementation of a fast RNS multiplie   | r192 |

|    | 9.4  | Hardware accelerator for the elliptic curve ECC25519                 | 192  |

| 10 | Futi | ure Work                                                             | 193  |

#### 10 Future Work

# List of Figures

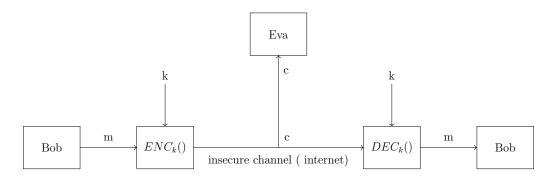

| 3.1  | Communication between parties using symmetric cryptography over<br>an insecure channel | 28       |

|------|----------------------------------------------------------------------------------------|----------|

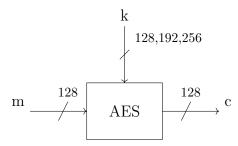

| 3.2  | General use of AES in encryption mode.                                                 | 20<br>29 |

| 3.3  | AES input array as an initial state.                                                   | 30       |

| 3.4  | Matrix representation for a state in AES                                               | 30       |

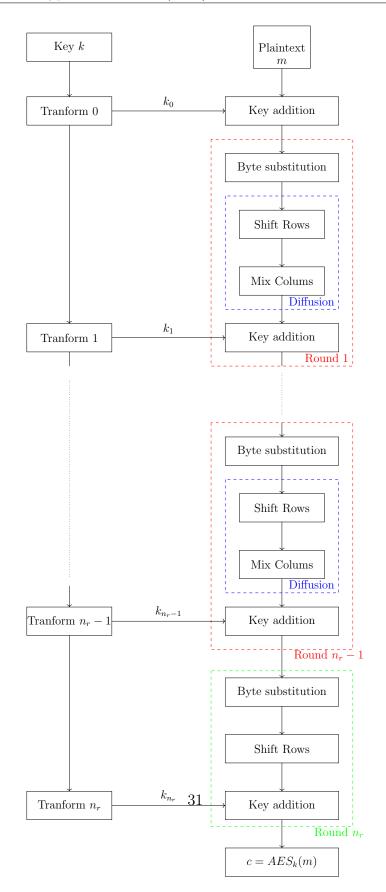

| 3.5  | AES encryption diagram                                                                 | 31       |

| 3.6  | Shift Rows (SR) input state.                                                           | 33       |

| 3.7  | Shift Rows (SR) output state.                                                          | 34       |

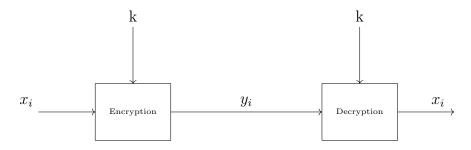

| 3.8  | Electronic codebook operation mode (ECB)                                               | 36       |

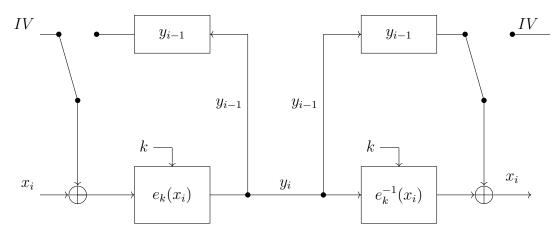

| 3.9  | CBC block diagram for encryption and decryption.                                       | 38       |

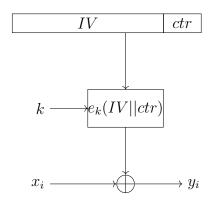

| 3.10 | Counter mode general diagram                                                           | 39       |

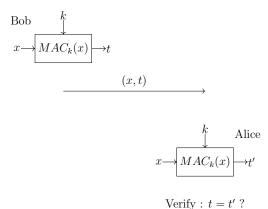

| 3.11 | Message authentication codes general diagram and verification $\ldots$ .               | 40       |

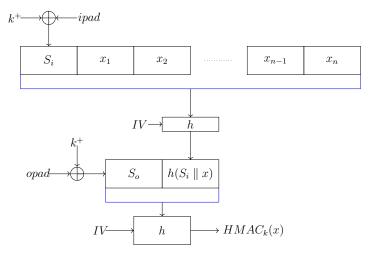

|      | HMAC diagram                                                                           | 42       |

|      | MAC implementation based on CBC operation mode                                         | 43       |

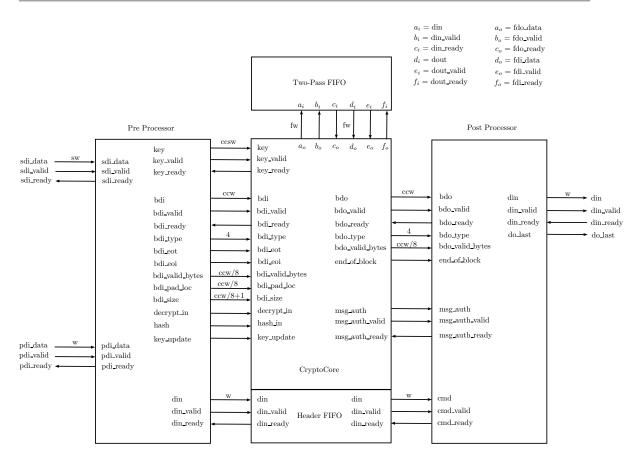

| 3.14 | Architecture diagram for single pass core used in AEAD by GMU                          | 50       |

| 4.1  | Two different four input LUTs                                                          | 63       |

| 4.2  | LUT with register and $XOR$                                                            | 63       |

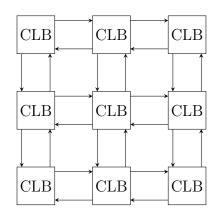

| 4.3  | FPGA Island connection between CLBs                                                    | 64       |

| 4.4  | Nearest neighbor structure                                                             | 64       |

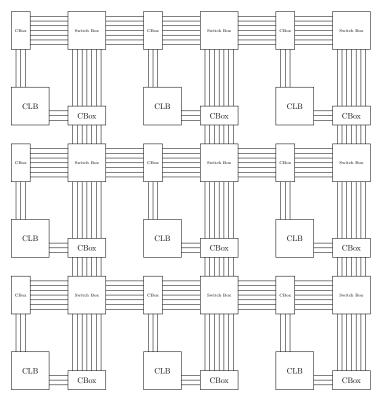

| 4.5  | Logic blocks in an island fashion with connection block and switch                     |          |

|      | boxes in the same architecture                                                         | 65       |

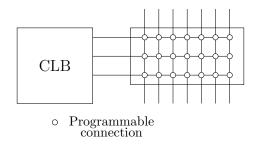

| 4.6  | Programmable connection block                                                          | 66       |

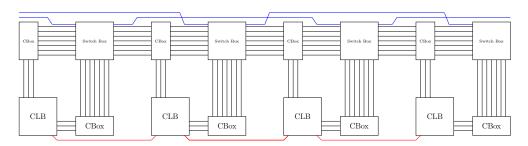

| 4.7  | Hybrid structure of nearest neighbor and segmented structure                           | 66       |

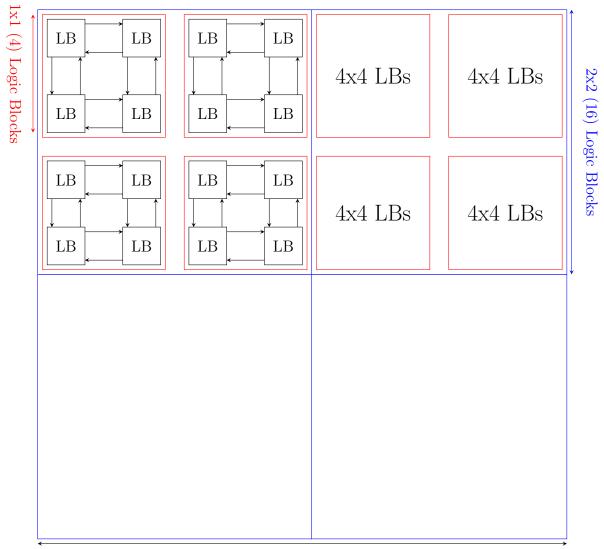

| 4.8  | Hierarchical structure with a cluster of logic blocks                                  | 67       |

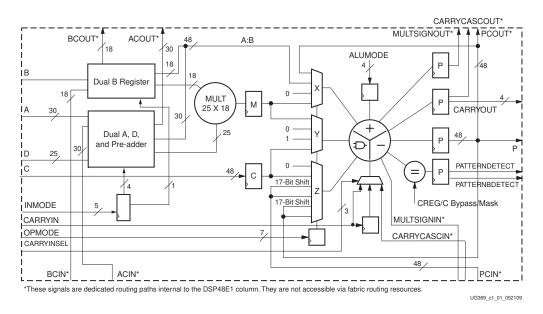

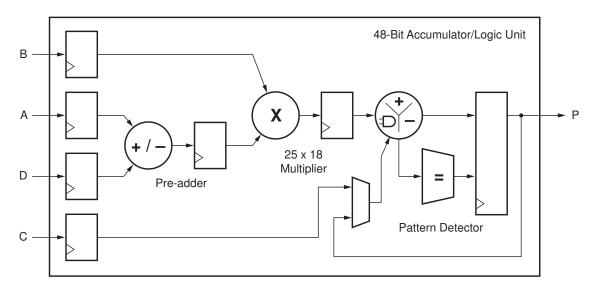

| 4.9  | DSP48E1 architecture.                                                                  | 68       |

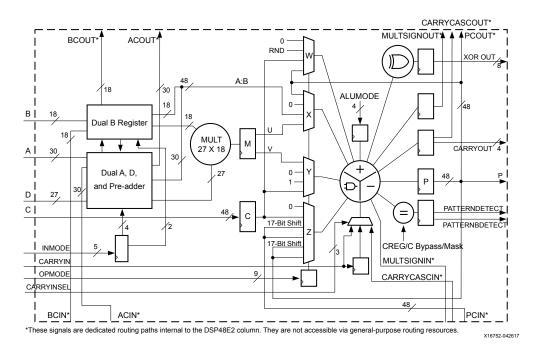

| 4.10 | DSP pipeline configuration window                                                      | 70       |

| 4.11 | DSP48E2 internal architecture                                                          | 72       |

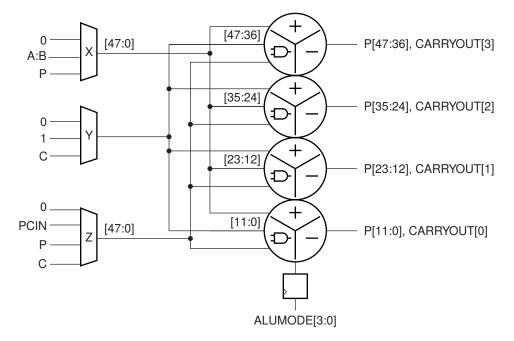

| 4.12       | DSP interconnection                                                                                                                                                                                                                                      | 73  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.13       | Internal ALU found inside a DSP slice                                                                                                                                                                                                                    | 74  |

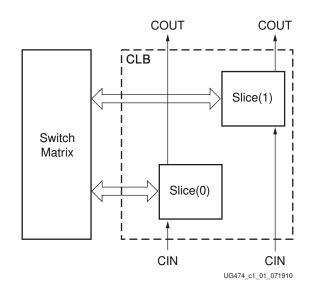

| 4.14       | CLB internal arrangement and interconnection matrix.                                                                                                                                                                                                     | 76  |

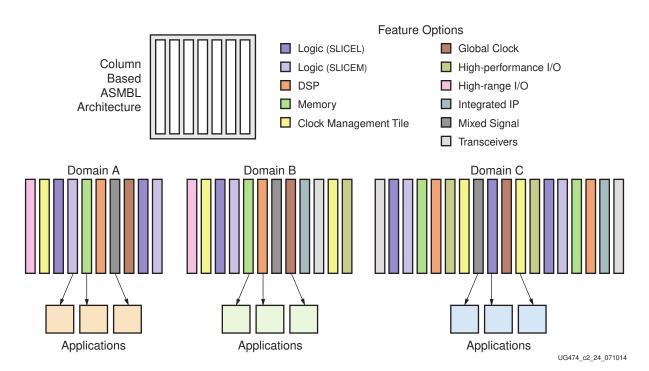

| 4.15       | ASMBL architecture with components as columns.                                                                                                                                                                                                           | 77  |

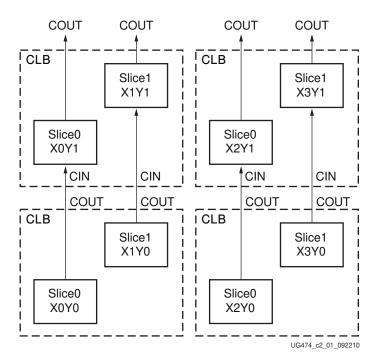

|            | CLBs and Slices with Carry inputs and outputs                                                                                                                                                                                                            | 79  |

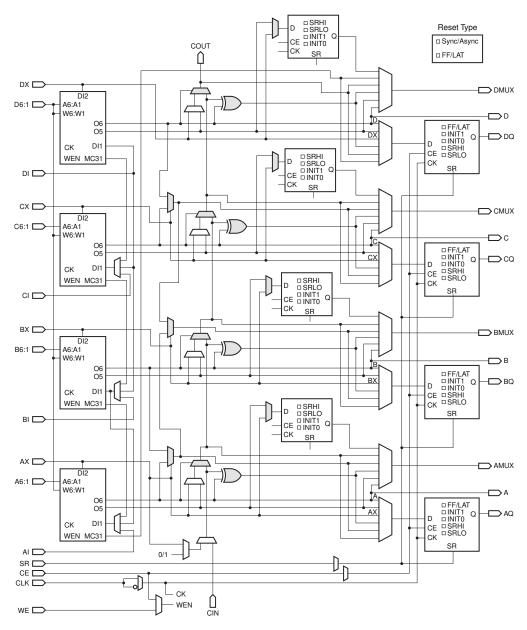

| 4.17       | Slice M architecture.                                                                                                                                                                                                                                    | 80  |

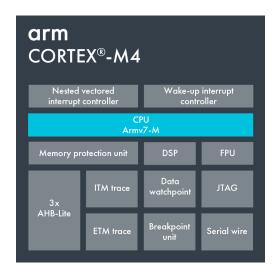

| 4.18       | ARM M4 general specs                                                                                                                                                                                                                                     | 82  |

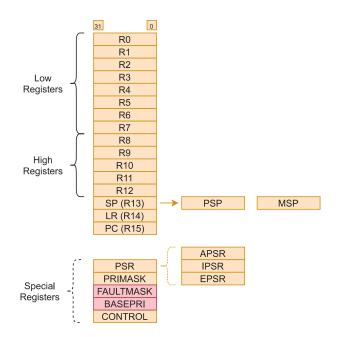

| 4.19       | ARM general purpose registers                                                                                                                                                                                                                            | 83  |

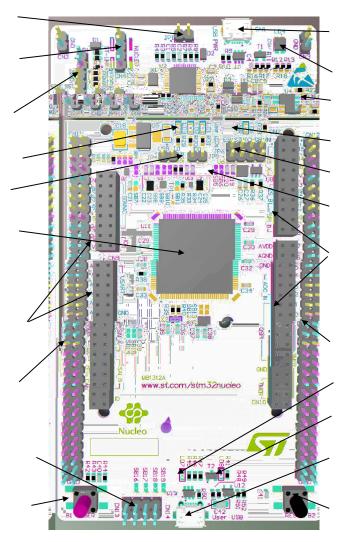

| 4.20       | ST Nucleo-144 board characteristics                                                                                                                                                                                                                      | 85  |

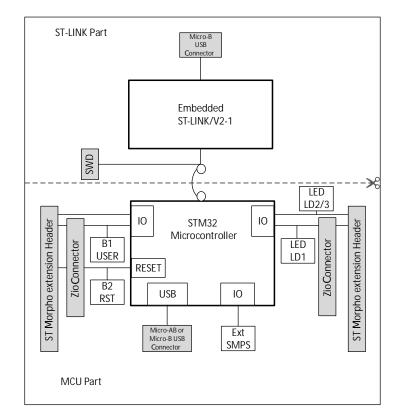

| 4.21       | ST Nucleo-144 schematic with ST-Link.                                                                                                                                                                                                                    | 86  |

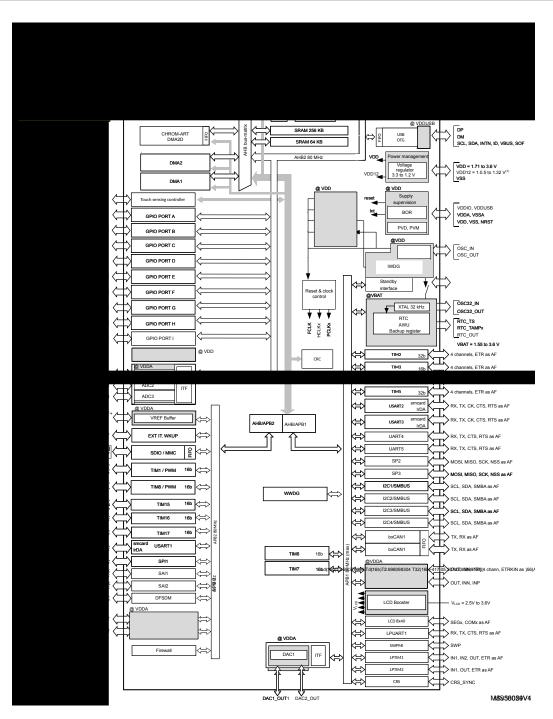

| 4.22       | STM32L4A6ZG ARM microcontroller internal architecture                                                                                                                                                                                                    | 87  |

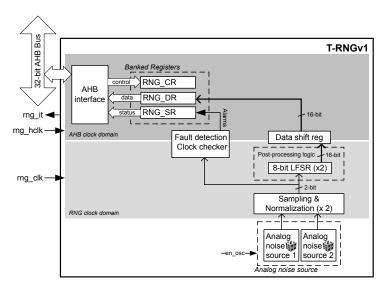

| 4.23       | Random Number Generator (RNG) embedded in STM32L4A6ZG                                                                                                                                                                                                    | 89  |

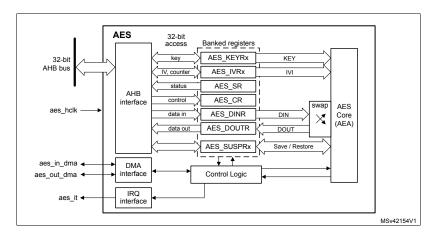

| 4.24       | AES block diagram                                                                                                                                                                                                                                        | 90  |

| 5.1<br>5.2 | Top-level block diagram of LWC core (based on the scheme found at [69]). Here, sw= external key width, w= external data width, ccsw= internal key width and ccw= internal data width Block diagram for associated data processing and Tag generation for | 99  |

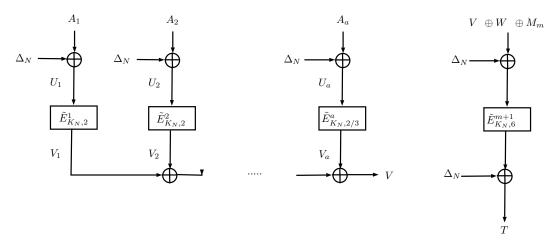

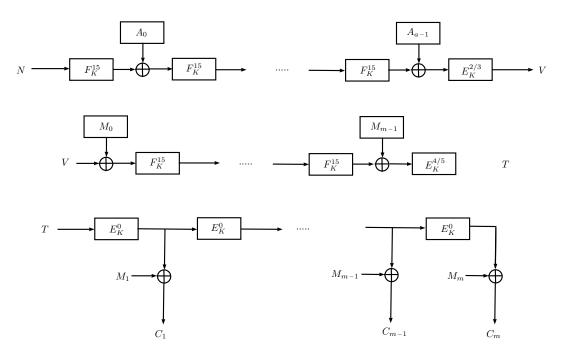

| 0.2        | LOCUS and LOTUS                                                                                                                                                                                                                                          | 101 |

| 5.3        | Block Diagram of LOTUS mode for encryption.                                                                                                                                                                                                              | 101 |

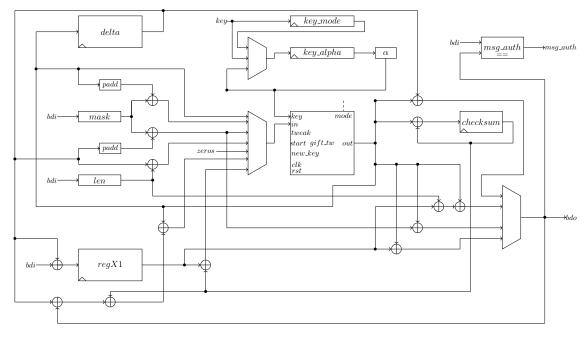

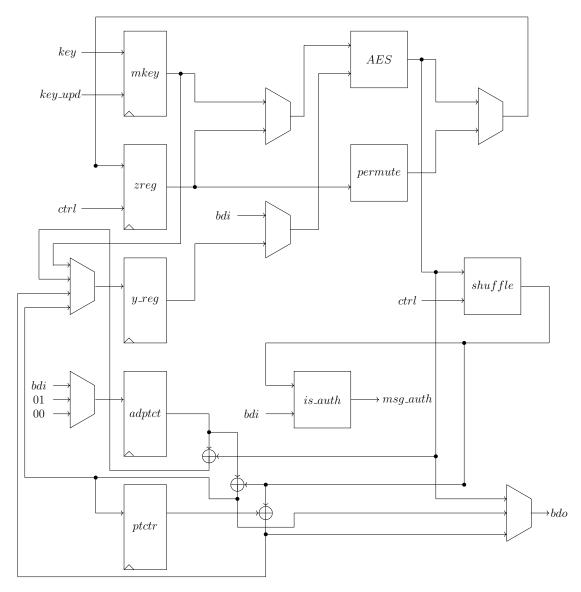

| 5.3<br>5.4 | LOTUS/LOCUS hardware architecture.                                                                                                                                                                                                                       | 103 |

| 5.5        | Block Diagram of LOCUS mode for encryption.                                                                                                                                                                                                              | 101 |

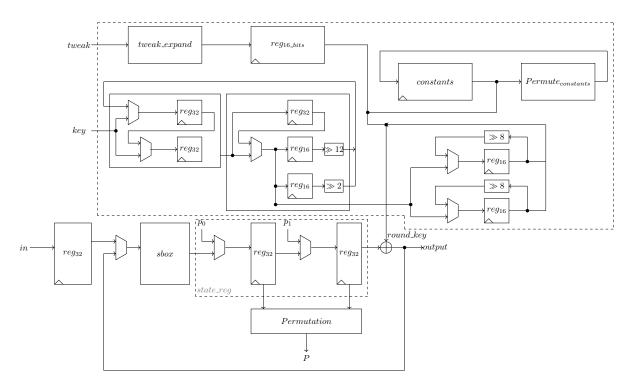

| 5.6        | tweGift-64 design implementation, for a 32-bit datapath.                                                                                                                                                                                                 | 100 |

| 5.7        | ESTATE Deterministic Authenticated Cipher.                                                                                                                                                                                                               | 108 |

| 5.8        | Architecture for ESTATE.                                                                                                                                                                                                                                 | 109 |

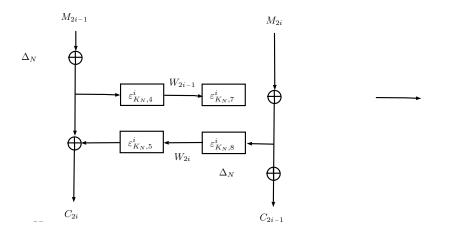

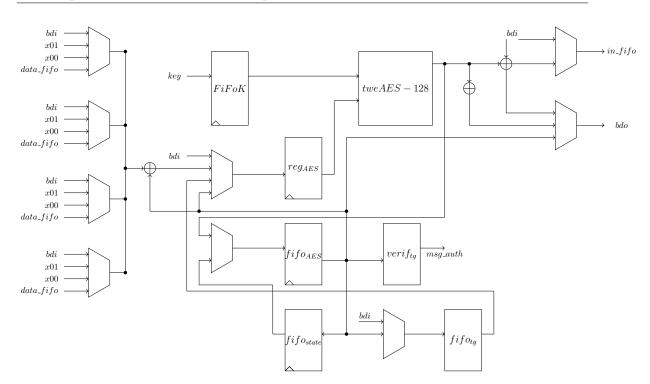

| 5.9        | Block diagram for COMET.                                                                                                                                                                                                                                 | 112 |

| 5.10       | COMET architecture for 8-bit and 32-bit.                                                                                                                                                                                                                 | 113 |

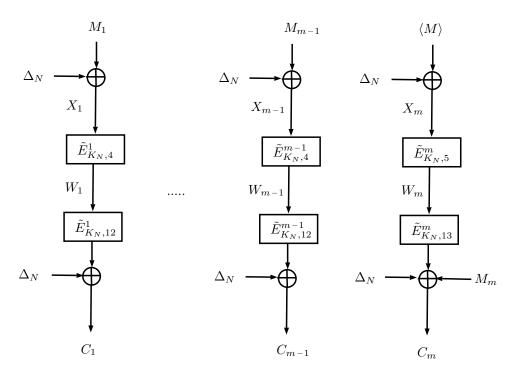

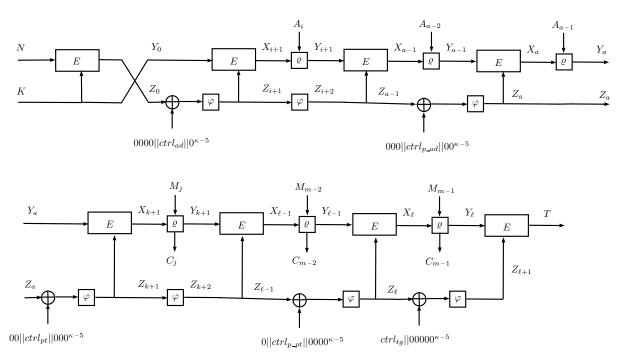

| 5.11       | Encryption version of Oribatida AEAD Algorithm (scheme based on                                                                                                                                                                                          | 110 |

| 0.11       | the found at $[16]$ )                                                                                                                                                                                                                                    | 115 |

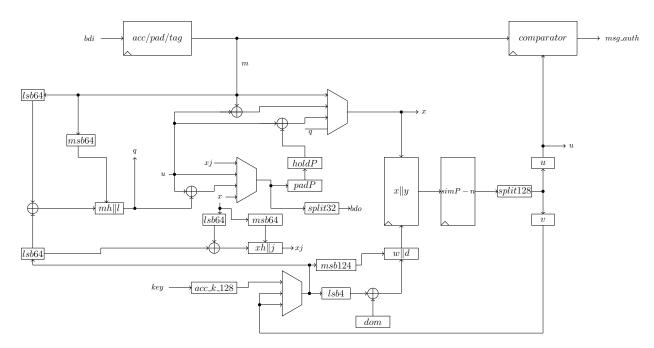

| 5.12       | LWC architecture for Oribatida AEAD.                                                                                                                                                                                                                     | 116 |

|            |                                                                                                                                                                                                                                                          |     |

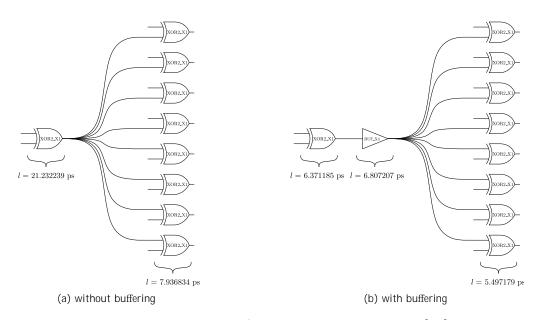

| 6.1        | Latency of 15nm NanGate (image from Speedy paper [80] page 518, figure 1)                                                                                                                                                                                | 127 |

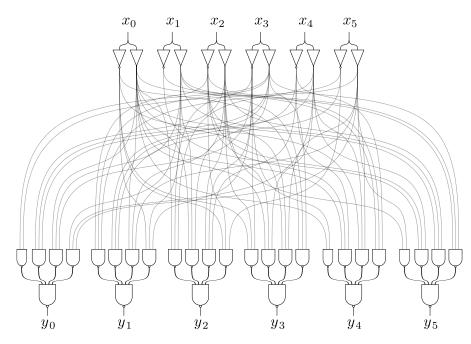

| 6.2        | Speedy 6-bit Substitution Box architecture with two-level NAND trees                                                                                                                                                                                     |     |

|            | and input buffers (image from Speedy paper [80] page 522, figure 2).                                                                                                                                                                                     | 128 |

| 6.3        | Speedy algorithm as block diagram (image from Speedy paper [80]                                                                                                                                                                                          |     |

|            | page $524$ )                                                                                                                                                                                                                                             | 129 |

|            |                                                                                                                                                                                                                                                          |     |

| 7.1        | Simplified DSP48E1 architecture                                                                                                                                                                                                                          | 151 |

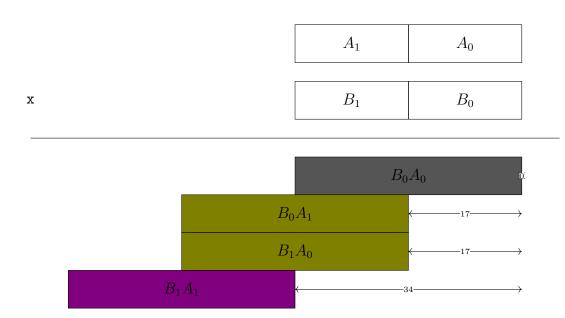

| 7.2  | Two-word schoolbook multiplication method                              | 155 |

|------|------------------------------------------------------------------------|-----|

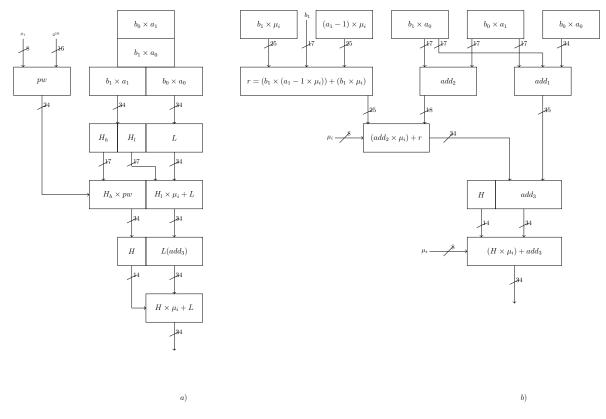

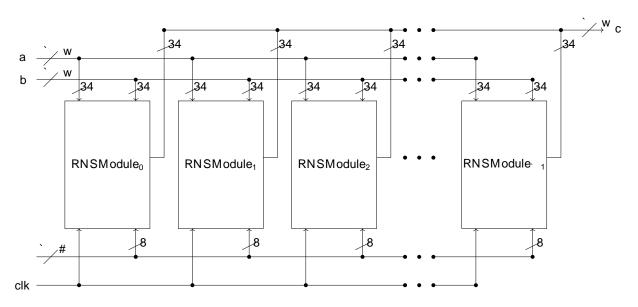

| 7.3  | Proposed RNS component-wise multipliers                                | 157 |

| 7.4  | RNSModule components array                                             |     |

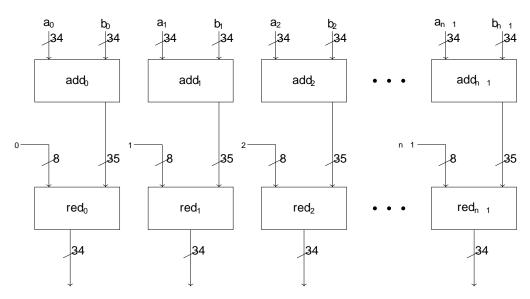

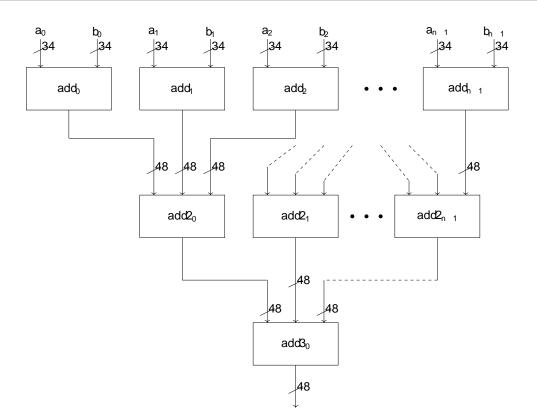

| 7.5  | Addition with reduction                                                | 160 |

| 7.6  | Addition tree                                                          | 161 |

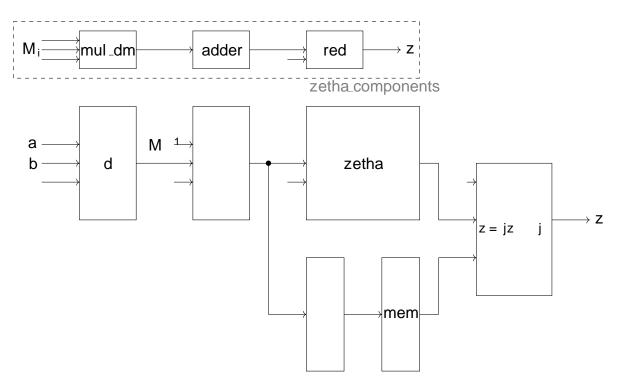

| 7.7  | General architecture performing the modular reduction of Algorithms 19 |     |

|      | and 22                                                                 | 162 |

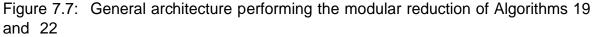

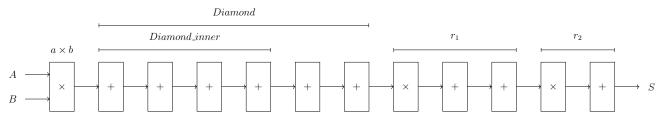

| 8.1  | Karatsuba diamond adder                                                | 171 |

| 8.2  | Karatsuba diamond with DSPs                                            | 172 |

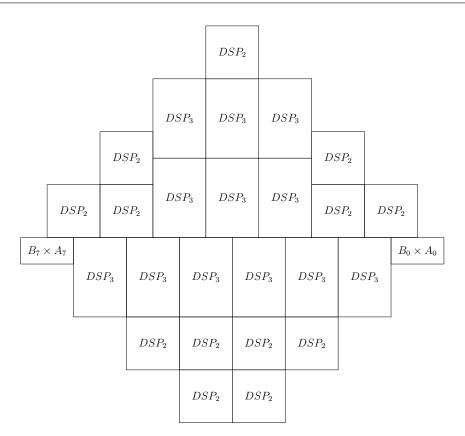

| 8.3  | Karatsuba diamond results                                              | 172 |

| 8.4  | Karatsuba diamond results from DSPs                                    | 173 |

| 8.5  | Diamond of the second level of DSPs results                            | 173 |

| 8.6  | 5                                                                      | 173 |

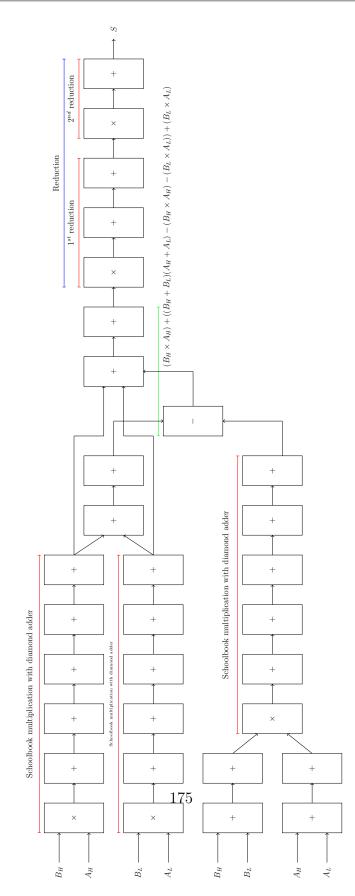

| 8.7  | Karatsuba multiplier critical path                                     | 175 |

| 8.8  | Diamond proposal for schoolbook method                                 |     |

| 8.9  | Diamond with DSPs                                                      | 178 |

| 8.10 | Diamond of results from the first level of additions                   | 178 |

|      |                                                                        | 179 |

| 8.12 | Diamond results from the second level of additions                     | 179 |

| 8.13 | Carry addition for the inner diamond in schoolbook                     | 179 |

| 8.14 | Addition of the three inner diamonds to get the final result           | 180 |

|      | Critical path schoolbook method                                        |     |

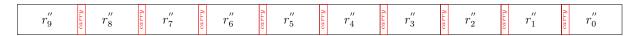

| 8.16 | Critical path RNS proposal                                             | 183 |

# List of Algorithms

| 1  | Addition of non-negative multi-precision integers             | 20  |

|----|---------------------------------------------------------------|-----|

| 2  | Subtraction of non-negative multi-precision integers          | 20  |

| 3  | Multiplication of positive multi-precision integers           | 21  |

| 4  | Karatsuba multiplication of positive multi-precision integers | 22  |

| 5  | Montgomery reduction <i>Redc</i> of multi-precision integers  | 23  |

| 6  | Euclid extended <i>gcd</i> of positive integers               | 24  |

| 7  | Chinese remainder                                             | 26  |

| 8  | AES algorithm with $Nb$ as the number of bytes processed      | 29  |

| 9  | Key generation in RSA.                                        | 54  |

| 10 | Simple RSA encryption.                                        | 54  |

| 11 | Simple RSA decryption.                                        | 55  |

| 12 | Simple RSA signature.                                         | 55  |

| 13 | Simple RSA signature verification                             | 55  |

| 14 | Simple Key generation on elliptic curves                      | 58  |

| 15 | Encryption "ElGamal" in elliptic curves.                      | 59  |

| 16 | Decryption "ElGamal" in elliptic curves.                      | 59  |

| 17 | ShiftColumns (SC) assembly code.                              | 132 |

| 18 | Montgomery Multiplication.                                    | 142 |

| 19 | RNS Modular Reduction [64]. $\ldots$                          | 147 |

| 20 | RNS Jeljeli Modular Reduction.                                | 150 |

| 21 | Basic RNS reduction module.                                   | 154 |

| 22 | RNS Montgomery Modular Reduction in HW                        | 156 |

# List of Tables

| $\begin{array}{c} 1.1 \\ 1.2 \end{array}$ | Classification and characteristics                                                                                   | 7<br>10    |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| $3.1 \\ 3.2$                              | Substitution Box represented with hex values                                                                         | 33<br>47   |

| 4.1<br>4.2                                | Summary of the difference between characteristics of the DSP48E1<br>and DSP48E2                                      | 75<br>75   |

| $5.1 \\ 5.2$                              | Valid segments in LWC API communication protocol Utilization of resources, throughput and TPA for implemented archi- | 98<br>117  |

| 5.3                                       | tectures on the xc7a12tcsg325-3 FPGA                                                                                 | 117        |

| 5.4                                       | Comparison of our LWC implementations regarding to the existing literature.                                          | 113        |

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Speedy 6-bit Substitution Box                                                                                        | 129        |

| 6.3                                       | of the bock $i$                                                                                                      | 131        |

| 7.1                                       | embedded instructions                                                                                                | 135<br>164 |

| 7.2                                       | Total resources of both implementations                                                                              | 165        |

| 7.3 | Comparative table with total memory required                   | 166 |

|-----|----------------------------------------------------------------|-----|

| 8.1 | Karatsuba multiplication with reduction, resources, and speed  | 185 |

| 8.2 | SchoolBook multiplication with reduction, resources, and speed | 185 |

| 8.3 | Adder with reduction, resources, and speed                     | 186 |

| 8.4 | Subtraction with reduction, resources, and speed               | 186 |

# Chapter 1 Introduction

Since the beginning of modern societies, security has been a necessary practice to protect sensitive information; otherwise, if that information becomes discovered by an opponent or adversary, it could compromise the security of a society, system, and even the user's health.

In ancient Rome, the emperor Julio Caesar put into practice a method to encrypt the information he wanted to send to his generals by performing a shift on the alphabet to send confidential information to them. If an opponent intercepts an encrypted letter, she cannot decrypt it; the encryption used is Caesar method encryption.<sup>1</sup>."

Miniaturization and technological advances help developing new devices with computational power like those used in Wireless Sensor Networks (WSNs) and the Internet of Things (IoT). These devices have embedded a small computer with constrained resources as a primary processing system. Usually, these devices assist humans with computational power embedded in everyday objects [122] like a cup, microwave, refrigerator, Tv, Etc. Likewise, they communicate through a ubiquitous network to recompile information from the environment. In this scenario, the user can perform actions through an interface to modify the environment behavior, such as turning on/off lights or using any other device to perform any action the user wants, depending on the device's capacities [116].

Ubiquitous computing involves a large-scale deployment of embedded devices in different areas and scenarios like e-healthcare, farming, smart home, and smart cities. Nevertheless, the security aspects in different applications as performance and low

<sup>&</sup>lt;sup>1</sup>https://es.wikipedia.org/wiki/Cifrado\_C%C3%A9sar "reviewed on 25/10/21"

power consumption, are essential [100]. Therefore, it is necessary to help ubiquitous computing to improve its security, and cryptography is the ideal science that protects data and information against no authorized third parties [85, 126].

Cryptology is a general area that comprises two main sub-areas. The first one is cryptography, which is in charge of protecting data and communications from third parties, and cryptanalysis breaks the security of a cryptographic system and helps to ensure that a cryptographic system is secure; the most relevant security aspects are

- Confidentiality: the information remains secret against third parties.

- Authentication: an authorized party can generate and access an information source.

- Data Integrity: protect the information against third parties modifications.

Lightweight cryptography [103] becomes a subarea of cryptography, focusing on algorithms oriented for devices with constrained resources to protect data streamed or stored in these devices. One solution is using block ciphers since they show excellent performance on embedded devices and provide confidentiality and data integrity in the implemented devices [136, 128, 56].

When developing a new device or application, security is not prioritized in information systems; data integrity or secure communication with other systems or devices is not essential. Although therefore, developing co-processors to improve the device's security and secure the sensitive information it manipulates and stores inside itself is a must. The developers must always be aware of the resources available and remember that the application could need more resources than those available for cryptography solutions.

The constrained resource devices used by Wireless Sensor Networks and the Internet of Things; are deployed in hostile environments where an adversary can access them and their data completely. In this scenario, the adversary can attack devices directly to obtain their secret information. Those attacks are known as side-channel attacks, which measure the power consumption of a device when it performs a cryptography task, for example, the encryption of a block of data. Unfortunately, implementing cryptographic algorithms does not warrant a countermeasure against these attacks. An inadequate implementation and poor countermeasures allow attackers to get information about the devices and sometimes complete access and control to confidential data. Today there are more communication scenarios using devices with constrained resources; these include tasks performed by applications that use devices such as RFID tags, sensors, and wireless sensors, all of them over different applications like healthcare, and the Internet of Things (IoT), among some high-speed devices like regular processors and servers with a large number of resources available. Constrained resource devices are typically present in these wireless environments, and the sensitive data exchanged among them demands security services such as confidentiality, integrity, and authentication. Unfortunately, public-key cryptography is not feasible due to its highest hardware requirements and the computational power needed to run the algorithms in this scope, and their use is focused on high-speed devices like FPGAs due to their speed and specialized characteristics.

An efficient and high-performance way to provide some of the previously listed services is by implementing an authenticated encryption algorithm with associated data (AEAD), which reduces resources on constrained devices and improves the versatility of high-speed implementations. However, the standard cryptographic algorithms to provide these services are unsuitable for constrained resource devices due to the same hardware and computational power requirements. Therefore, public-key cryptography is present on almost all devices with no restrictions and can handle data harvested from constrained devices, and due to the high speed achieved by high-speed devices, public-key cryptography is used in this kind of scenario.

Hardware restrictions have several drawbacks regarding the area usage (resources available) and power consumption that needs to be solved in constrained devices used in wireless environments without any permanent power source, and it is not always possible to ensure enough power is available.

These devices can use a battery (or another portable power source) with a limited amount of stored energy becomes a restriction to use traditional cryptography algorithms to provide security services. Also, thinking in lightweight cryptography, the developers must reduce the duty cycle of the implemented algorithms for a limited amount of time to increase the power source lifetime available for other tasks.

The deployed devices are in heterogeneous places where the area used by the cryptographic algorithms is constrained. Therefore, their footprint should be minimal to perform all tasks with low power consumption to increase the time to perform the device's principal tasks online. Constrained resources in ubiquitous environments need lightweight cryptography primitives to offer security services as the device application requires. Additionally, other tasks (such as the data exchange) would prioritize using the available resources (storage if available, and other essential tasks), leaving limited resources available for cryptographic primitives. On the other hand, high-speed devices can handle many tasks thanks to their available sources, allowing them to keep running as long as possible to perform critical tasks.

A lightweight cryptography primitive should use the lowest possible hardware resources with low power consumption without adding more hardware complexity or resource consumption, leaving most resources available for other critical tasks. On the other hand, public-key cryptography and traditional symmetric-key cryptography can take advantage of the resources available on high-speed devices to handle the data encryption and other security services required or queried from constrained devices and other sources.

#### 1.1 Motivation

Recently, constrained devices in different applications have grown in ubiquitous environments, and devices with computer capacity in reconfigurable hardware and heterogeneous scenarios use sensors and actuators. However, most of the algorithms developed with a lightweight focus, known as Lightweight cryptography (LWC), are focused on being used in constrained resources devices. Therefore, the meaning of "lightweight" is not always the same because they must cover several points, like reducing power consumption and the area used by the cryptography hardware. On the other hand, high-speed implementations are required to handle the communication of large amounts of constrained devices and to provide some expensive security services.

#### 1.2 Problem statement

The suitable cryptographic algorithms for lightweight applications mark a trend in lightweight cryptography. They offer security to tiny electronic devices with computational power, like wireless sensor networks (WSN) and Internet Things (IoT) devices. Moreover, this aims at applications where devices have a limited power source, like a battery. Therefore, high-speed hardware always is needed to handle a large amount of data and to provide security services to other devices. The area used by any device and its internal components to perform its tasks directly affects the power consumption at run time because this represents the required power by the device to perform any task in a time-lapse.

Consequently, if the total area of the design and the internal components is small enough on area consumption, it shows a growing power consumption on the same tasks because the implemented algorithm requires more run time to perform cryptography tasks.

The works of [45, 88] show that some implementations could use a large amount of area, and sometimes these implementations are more energy-efficient when running lightweight algorithms. However, this trade-off implies no area restrictions and execution time due to the small number of plaintexts the crypto-core needs to process, i.e., power consumption is the primary goal.

On the other hand, other works focus on power efficiency, as shown in work realized by [136], and some others aim for better performance regarding the area used by the implemented algorithm.

#### 1.3 Objectives

To implement lightweight cryptography (LWC) algorithms on various constrained resource devices, focus on high-speed hardware and its characteristics to develop both high-speed and low-speed hardware. Moreover, perform a performance analysis of the implemented algorithms on the processors, micro-controllers, and FPGAs used.

- Implement public-key algorithms on high-speed devices focusing on key pair generation and basic mathematical operations.

- Implement hardware-oriented algorithms using techniques to improve the algorithm's performance on embedded devices.

- Implement LWC algorithms by being aware of the resources focus on the low-speed microcontrollers and FPGAs.

- Implement and design a lightweight and public-key cryptography crypto-processor on FPGA.

- Test our proposals and implementations.

- Compare the performance of our implementations and proposals against others from state-of-the-art.

#### 1.4 State-of-the-art

Lightweight Cryptography provides security solutions to devices with constrained resources<sup>1</sup>. In addition, the academic community develops research that includes the implementation of cryptography standards, design, and analysis of cryptography algorithms and protocols.

Its focus is on embedded devices like wireless sensor networks, RFID devices, and IoT; the evolution of IoT implies the interconnection of many embedded devices, usually with constrained resources and their interaction with the users [49, 48]. IoT encompasses all the above because of its similarities to the embedded computer [62].

It focuses on embedded devices with constrained resources in wireless sensor networks, RFID devices, and IoT. Those scenarios imply the interconnection of many embedded devices, and their interaction with the users [49, 48]. Also, the constrained resources devices encompass all the above scenarios due to their similarities to a traditional computer [62].

As a general description, the Oxford English Dictionary defines the IoT as development where daily objects have a network connection that allows sending and receiving data to help users improve their daily activities<sup>2</sup>.

The target devices usually have restricted resources by their limited computing power, RAM, ROM, and others. In addition, these devices have a microcontroller as a central processing unit. Another kind of processor used is system-on-Chip which has integrated all modules that conform a complete computer into an integrated circuit. Another kind of processing unit used is the ARM microprocessors and Field

<sup>&</sup>lt;sup>1</sup>http://nvlpubs.nist.gov/nistpubs/ir/2017/NIST.IR.8114.pdf (reviewed 25/Oct/2021)

<sup>&</sup>lt;sup>2</sup>https://www.owasp.org/index.php/OWASP\_Internet\_of\_Things\_Project (reviewed 10/Nov/2021)

Programmable Gate Array (FPGA); the FPGAs consist of a logic block as a basic reconfigurable unit consisting of LUT's (lookup tables), Flip-Flops and multiplexers [134, 57, 2, 95].

The main characteristics of constrained devices are their limited resources. In some scenarios, they use batteries as a power source; they can acquire data from the environment by using sensors and send the data obtained to other devices using Wi-Fi, Ethernet, or Bluetooth communication;

Besides, they can perform actions in the environment, like turning on something or activating any other device to perform actions in the environment. Shortly, there is a list of some microcontrollers and microprocessors used in constrained devices.

- Microcontrollers of 8, 16, and 32 bits like AVR (Microchip), for example, ATMega328P (Used by Arduino UNO platform) or the model ATM2560.

- The SoC Snapdragon 32-bit ARM of 28 nm is from the Nvidia Tegra family with ARM and CUDA technologies like Tegra 3, TK1, and TX1.

- The 32-bit ARM processors are the most used in platforms of IoT; for example, minicomputers and Raspberry Pi platforms.

The constrained devices classification shown in table 3 presents three classes with general characteristics.

|           | Speed        | Ram          | Rom         | Power    |

|-----------|--------------|--------------|-------------|----------|

| Class I   | 4 Mhz        | 1 KB         | 4 - 16 KB   | 1.5mA    |

| Class II  | 4 - 8 Mhz    | 4 - 10 KB    | 48 - 128 KB | 2 - 8 mA |

| Class III | 13 - 180 Mhz | 256 - 512 KB | 4 - 32 MB   | 40 mA    |

Table 1.1: Classification and characteristics

Table 1.1 shows the three classes in the state-of-the-art, but it must be taken into account that there is a fourth classification to the constrained devices which will not

have kind of mention in this work. The devices in class I have the most constrained resources; all devices barely run a minimal operating system.

Devices with many more resources in the III class can run more sophisticated operating systems and even Java virtual machines. Finally, the devices with enough resources to perform "complex" tasks belonging to class II are the most commonly used for sensor nodes and IoT[82].

The IoT uses microcontrollers and microprocessors in the second class; they are an essential technology for the future for their capacity to get data from the environment without needing an electric network, for example, automobiles, smart homes, industry, to monitoring e-Healthcare, and farming.

When a developer designs an IoT device, the are restrictions like reducing power consumption when performing any task for longer battery life. In addition, the devices must be low-cost, and characteristics directly impact the security offered on these devices depending on the application<sup>1</sup>.

#### 1.4.1 Security on constrained devices

As previously mentioned, IoT has become a vital part of human life; besides, it is not well-defined or entirely secure. Today, all the proposed architectures must face many problems and challenges in security, and the technologies used in IoT do not have an acceptable security level.

Security in practice for constrained devices is essential because many attacks like Distributed Deny of Service (DDoS) exist. Those direct attacks on these devices cause serious security problems such as data alteration, privacy risks, and data modification.

The security challenges on constrained devices are due to their less complex nature, and traditional security aims at gadgets with more resources. The current cryptography implemented ranges from the implementation of block cipher algorithms to the development of alternative solutions like authentication servers, key-servers<sup>2</sup>, Some Lightweight algorithms like PRESENT, PHOTON, and SPONGENT included in standards ISO (ISO/IEC 29192-5:2016) [9]. The following list shows some detected

<sup>&</sup>lt;sup>1</sup>https://www.nist.gov/itl/applied-cybersecurity/iot-cybersecurity-considerations

<sup>&</sup>lt;sup>2</sup>https://www.owasp.org/index.php/Guide\_to\_Cryptography

security problems on these systems [62]..

- Authentication: Used to identify users and devices over a heterogeneous network that uses traditional cryptography like certificates or the Public-Key-Infrastructure PKI on constrained resource devices difficult.

- Confidentiality: ensures that the information remains secret against third parties; a block cipher ensures that the only one who owns the secret key can access the data.

- Fault tolerance: if a node fails or gets jeopardized, the system must provide the security services available to the other nodes or users, i.e., the whole system remains running.

- Anonymity: users can hide their identity and the sensitive information they want, i.e., any user remains anonymous while interacting with the system.

Previous items consider some vulnerabilities in Open Web Application Security Project (OWASP). In addition, there is a section oriented to IoT<sup>1</sup> even though there is a guide that emphasizes some security aspects to take into account for the developers, manufacturing companies of IoT devices, and the public consumer<sup>2</sup>.

Some lightweight cryptography primitives such as block ciphers, hash functions, stream ciphers, and message authentication codes have been proposed during the past decade. They offer some advantages in performance against traditional cryptography standards; also, there are lightweight block cipher proposals with some benefits over the National Institute of Standards and Technology (NIST) Advanced Encryption Standard (AES) standard [46].

Just one algorithm cannot satisfy all security requirements, and weak points have priority to ensure the security of the constrained device. Below is a list of some options that offer one security aspect to implement as the application requires.

• Elliptic curves cryptography (ECC): Digital signatures to ensure the data comes from a trusted party and the possibility to share a secret between two parties.

- Two-step authentication: offers user identification and authentication when logging into the system.

- Maintenance log: provides security audits, non-repudiation, and intruder detection.

| Layer             | Security challenges                                                  | Security requirements                                                             |  |

|-------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| perception layer  | Resource restrictions,<br>DoS vulnerable and interference            | Lightweight encryption,<br>sensor data protection,<br>Key agreement               |  |

| Network layer     | Network congestion,<br>virus spread<br>DDoS attacks                  | Authentication and identity<br>encryption<br>anti DDoS<br>Secure communication    |  |

| Support layer     | Large data processing,<br>Data filtering                             | secure communication<br>secure computing                                          |  |

| Application layer | Data privacy and leakage<br>Access control<br>Application challenges | Key agreement and authentication<br>Privacy protection<br>Security administration |  |

Table 1.2: Layers, challenges, and requirements in security

Table1.2 shows a compilation of challenges for each layer and every security requirement for each one [1, 65, 121, 137].

The perception layer consists of hardware devices; the main problem in this layer is the constrained resources, low computational power, and storage. It also must have low power consumption while running any algorithm; this requires a high level of encryption techniques or similar solutions with unfavorable performance impact in practice.

Network layer: this layer faces congestion caused by lots of data traffic, and the IoT cannot implement some secure communication mechanisms; on the other hand, it already has some others implemented like TLS/SSL, IP sec, anti-DDoS, and others [127].

Support layer: cloud computing and other use security applications at the system architecture or application levels. Therefore, this layer uses the best encryption

algorithms, protocols, antivirus, and string security techniques.

Application layer: deals with data privacy, access control mechanisms, and data leakage because data sharing is the most crucial characteristic in IoT environments where the data is stored or shared between two or more parties.

#### 1.4.2 Security on high-speed devices

As a difference against the constrained resource devices, traditional cryptography focuses on high-speed implementations taking advantage of the resources available on regular processors like Intel and AMD processors, using technologies like intrinsic instruction sets and large-size registers embedded in the processors. Therefore publickey cryptography requires basic mathematical operations to generate and create a shared secret between two parties.

The mathematical operations required consist of additions and multiplications, and these last operations require a large number of clock cycles to complete just one; this is the reason why constrained devices are not suitable to handle public-key cryptography, but high-speed devices can offer new ways to implement basic operations to perform faster solutions on this area.

Many works focus on implementing just the basic operations to improve the performance of public-key algorithms on hardware; some applications are RSA and ECDH algorithms, and others are out of the scope of this thesis work. The paper [40] presents the modular exponentiation using Intel's AVX512 intrinsics set available on some of the 10th series families and newer. Work [7] computes the reduction modulo  $\mathcal{F}$  using a multiplier based on the Karatsuba algorithm. One application of RSA is presented in work [47], which implements an RSA Key generation protocol focusing on a two-party setting. Also, they propose an approach for multiplying two large integers. In the same scope, the Montgomery for reduction algorithm presented later in this thesis focuses on ARM devices. This work given in [22] uses the mentioned algorithm to implement isogeny-based cryptography on ARM architectures. Finally, the work [31] presents a scheme of Homomorphic encryption proposal using real numbers and uses the Residue Numeric System RNS shown later in this thesis work to improve the performance of their implementation.

#### 1.5 Summary

This chapter summarizes the challenges and activities carried out in this thesis; it also offers the objectives and a brief state-of-the-art along with the problem statement, which is the primary motivation for this thesis work. Furthermore, restricted device types are classified based on their features, resources, and applications. Also, it presents requirements of traditional cryptographic algorithms and some implementations and applications on high-speed devices like regular processors and FPGAs.

# Part I Theoretical Background

# Chapter 2 Preliminaries

In this first part of this thesis works, the theoretical background needed to develop the works presented in the following chapters presents a brief introduction to definitions of the theories used to develop this thesis work focused on public-key cryptography and symmetric key cryptography as well as the mathematical background needed to understand the designs developed in the chapters 7 and 8.

# 2.1 Mathematical Background

This chapter shows the essential mathematical background to understand and develop cryptography systems. Then, we use this knowledge to create general cryptography systems in hardware and software.

Usually, using the integer ring  $\mathbb{Z}$  is the mathematical basis of cryptography. Once we can compute with integers is possible to build on top of them fields, elliptic curves, and even more complex objects. To perform faster integer arithmetic is why the hardware plays an important role when implementing arithmetic on computing systems.

# 2.2 Algebra

Here we present some abstract algebra fundamentals to understand the Public-key algorithms presented later in this thesis work.

#### 2.2.1 Groups

As presented in [34] chapter 2, section 2.1, a group gets defined by the following.

Given a set S, a composition law  $\times$  of S into itself is a mapping from the Cartesian product  $S \times S \to S$ , Common notations for the image of (x, y) under this mapping are  $x \times y$ ,  $x \cdot y$  or simply xy. When the law is commutative, i.e., when the images if (x, y) and (y, x) under the composition law are the same  $\forall x, y \in S$ , it is customary to denote it by "+".

Another definition says: A group G is a set with a composition law  $\times$  such that,

- $\times$  is associative, that is  $\forall x, y, z \in G$  we have (xy)z = x(yz)

- $\times$  has a unit element e, i.e.,  $\forall x \in G$  we have xe = ex = x

- for every  $x \in G \exists y$ , an *inverse* of x such that xy = yx = e.

#### Remarks

- 1. The group G is *commutative* or *abelian*, if the composition law is commutative. As previously mentioned, the law often gets denoted by + or  $\oplus$  and the unit element by 0 for this case.

- 2. The unit of a group G is necessarily unique and is the inverse of an element x that is denoted with  $x^{-1}$ . if G is commutative the inverse of x gets denoted by -x.

- 3. The order or cardinality of a group G is finite it its order is finite.

**Example:** Let  $x \in G$ . The set  $\{x^n \mid n \in \mathbb{Z}\}$  is the subgroup of *G* generated by *x*. It is denoted by  $\langle x \rangle$

#### 2.2.2 Rings

Also, in the same book [34] section 2.1.2, chapter 2 present various definitions for rings; here, we present some of them and an example.

A ring R is a set together with two composition laws + and  $\times$  such that

• R is commutative respect to +

- $\times$  is associative and has a unit element 1, which is different from 0 of the unit +

- × is disruptive over +, that is  $\forall x, y, z \in R, x(y+z) = xy + xz$  and (y+z)x = yx + zx.

#### Remarks

- 1. The ring R is said to be *commutative*, if the law x is commutative.

- 2. A commutative ring R such that  $\forall x, y \in R$ , the equality xy = 0 implies that x = 0 or y = 0 is called *integral domain*.

**Example:** the set  $\mathbb{Z}$  of integers together with the usual addition and multiplication is a ring. The set  $\mathbb{Z}[X]$  of polynomials with coefficients in  $\mathbb{Z}$  together with the addition and multiplication of polynomials is a ring.

## 2.2.3 Fields

Once more, in the same book [34] in the same chapter 2 section 2.1.3, we found different definitions of Fields, but we only present some of them here.

A field K is a commutative ring such that every nonzero element is invertible.

**Example:** the set of rational numbers  $\mathbb{Q}$  with the usual addition and multiplication law is a field. The quotient set  $\mathbb{Z}/p\mathbb{Z}$  with the induced integer addition and multiplication is also a field for any prime number p.

## 2.2.4 Extension of elds

Usually, in cryptography, some operation becomes easier to implement using an extension of fields, allowing the creation of more complex arithmetic. Some properties of algebraic extensions of fields are presented from the book [34] chapter 2, section 2.2.1.

**De nition**: Let K and L be two fields, we can say that L is an *extension field* of K if there exists a field homomorphism K into L. Such an extension field is denoted by L/K.

Remark: as previously mentioned, a field homomorphism is always injective, so we

shall identify K with the corresponding subfield of L when considering L/K.

**Example:** let  $\mathbb{R}$  the field of real numbers with usual addition + and multiplication  $\times$ . Therefore,  $\mathbb{R}$  is an extension of  $\mathbb{Q}$ . Consider the element  $\sqrt{2} \in \mathbb{R}$  and the subset of  $\mathbb{R}$  of elements with the form  $a + \sqrt{2}b$  with  $a, b \in \mathbb{Q}$ . If we put for  $a + \sqrt{2}b$  and  $a' + \sqrt{2}b'$

$$(a + \sqrt{2}b) + (a' + \sqrt{2}b') = a + a' + \sqrt{2}(b + b')$$

(2.1)

and

$$(a + \sqrt{2}b) \times (a' + \sqrt{2}b') = aa' + 2bb' + \sqrt{2}(ab' + a'b), \qquad (2.2)$$

we can see that we obtain a field denoted by  $\mathbb{Q}(\sqrt{2})$ , which is an extension of  $\mathbb{Q}$ .

## 2.3 Integer arithmetic operations

As mentioned at the beginning of this chapter, Integer arithmetic is fundamental and must perform as efficiently as possible. Although modern computers operate with relatively large integers thanks to technologies like advanced vector extension (AVX) [81, 35] instruction set, we can design reliable components in hardware to perform the same operation presented here with better performance than software implementations.

Modern computers have highly optimized operations for single-precision integers. Therefore, they can perform the following functions from [34] chapter 10, section 10.1.3.

- Comparison of two singles return a boolean 0 or 1.

- Bitwise complement of a single u, that is  $\overline{u} = b 1 u$ .

- Bitwise conjunction, disjunction and exclusive disjunction of the singles u and v, that is respectively  $u \wedge v, u \vee v$  and  $u \oplus v$  used to denote XOR.

- The *right* and *left* shifts of t bits for a single u, denoted by  $u \gg t$  and  $u \ll t$  respectively, corresponding to  $|u/2^t|$  and  $u2^t \mod b$ .

Addition of two singles u and v results in a single w and a carry bit c equal to 0 or 1 so that the result is u + v = kb + w.

Subtraction of a single v from a single u, that is u - v, results in a single w and a carry c. If  $u \ge v$  then w = u - v and c = 0, otherwise w = b + u - v > 0 and c = -1, sometimes called *borrow* for its unsigned representation.

- Multiplication of two singles u, v results in a double size result  $w = u \times v$ .

- Division of a double size u by a single v, when the quotient  $q = \lfloor u/v \rfloor$  and the remainder  $r = u \mod v$  are both singles. This computes q and r simultaneously.

We must understand the basic facts of integers and computers to use large integers. For example, let  $b \ge 2$  an integer is known as *base* and sometimes *radix*, and it is possible to represent any integer u > 0 as the sum.

$$u = u_{n-1}b^{n-1} + \dots + u_1b + u_0 \tag{2.3}$$

provided  $0 \le u_i < b$  and  $u_{n-1} \ne 0$ . We call this representation the base b of u and is denoted by  $(u_{(n-1)}, \ldots, u_0)_b$ . witch each  $u_i$  as the digits of u. Finally the most significant digit is denoted by  $u_{n-1}$  and least significant by u, therefore, the length n of  $(u_{(n-1)}, \ldots, u_0)_b$  is denoted  $|u|_b$ .

In any digital system like a computer, the base b is a power of 2 stored as an internal sequence of 0 and 1, known as bits. So, also exists elementary operations on bits like the following:

- complement of x denoted by  $\overline{x}$ , if x = 0 then  $\overline{x} = 1$

- conjunction of x and y,  $x \wedge y$  the output is equal to 1 is both x, y equal 1.

- disjunction of x and y,  $x \lor y$  the output equals 1 if any of both are equal to 1.

- exclusive disjunction of x and y, known as XOR. The operation x xor y equals 1 if and only if exactly one of the values x, y equals 1.

#### 2.3.1 Addition and Subtraction

In the book [34] chapter 10, section 10.2 presents the addition algorithm used to add multi-precision integers; the same is presented here in the algorithm 1.

Algorithm 1 Addition of non-negative multi-precision integers

**Require:** Two *n*-word integers  $u = (u_{n-1}, \ldots, u_0)_b$  and  $v = (v_{n-1}, \ldots, v_0)_b$ . **Ensure:** The (n + 1)-word integer  $w = (w_n, \ldots, w_0)_b$  such that w = u + v,  $w_n$  being 0 or 1. 1:  $k \leftarrow 0$  [k is the carry] 2: for i = 0 to n - 1 do 3:  $w_i \leftarrow (u_i + v_i + k) \mod b$   $[0 \le w_i < b]$ 4:  $k \leftarrow \lfloor (u_i + v_i + k)/b \rfloor$  [k = 0 or 1] 5: end for 6:  $w_n \leftarrow k$ 7: return  $(w_n, \ldots, w_0)_b$

For the subtraction, we present the algorithm 2, just a simple change of sign in the algorithm 1 to provide (u - v) instead (u + v) equipped  $u \ge v$ .

Algorithm 2 Subtraction of non-negative multi-precision integers **Require:** Two *n*-word integers  $u = (u_{n-1}, \ldots, u_0)_b$  and  $v = (v_{n-1}, \ldots, v_0)_b$  such that u > v. **Ensure**: The *n*-word integer  $w = (w_{n-1}, \dots, w_0)_b$  such that w = u - v. [k is the carry]1:  $k \leftarrow 0$ 2: for i = 0 to n - 1 do  $w_i \leftarrow (u_i - v_i + k) \mod b$  $[0 \leqslant w_i < b]$ 3: [k = 0 or -1] $k \leftarrow |(u_i - v_i + k)/b|$ 4: 5: end for 6:  $w_n \leftarrow k$ 7: return  $(w_{n-1}, \ldots, w_0)_b$ [if k = -1 then u < v]

#### 2.3.2 Multiplication

The most critical process in any crypto-system is multiplication, the most timeconsuming part for many applications. Therefore the complexity parameter of a multiplication algorithm is essential for any complete arithmetic system. In this section, we present two multiplication algorithms Schoolbook method and Karatsuba.

#### School book

The simplest method known for at least four millennia [34].

#### Algorithm 3 Multiplication of positive multi-precision integers